第五章 直流參數測試

直流參數測試也稱DC參數測試。主要驗證Device的電壓與電流值。也就是說,先設定好量測的條件後,再量測電壓或電流。本章節,會介紹以下的幾項重要的直流參數測試項目。

- 輸入腳漏電流量測(IIH/IIL)

- 輸出腳高阻抗漏電流量測(IOZ)

- 耗電流量測(IDD)

- 輸出腳短路電流量測(IOS)

- 輸出腳電壓量測(VOH/IOH)

- 輸出腳電壓量測(VOL/IOL)

- 輸入二極體限壓參數

測試流程

測試流程(Test Flow)就是測試項目,依序逐一被執行的步驟。每一個測試項目,在執行的過程當中,待測物是否Pass或者Fail,都會被記錄及分類。當測試程式將整批Device測試完畢後,會產生一份測試結果,稱為Test Report或Test Summary Report。這份報告上,會有幾項重要訊息。(1)平均良率。(2)Device的描述。(3)測試時間、測試設備、測試人員。(4)測試數量。(5)好壞品數量及良率。(6)類別數量及百分比。(7)測式條件,例如測試溫度。(8)測試分類圖等等。

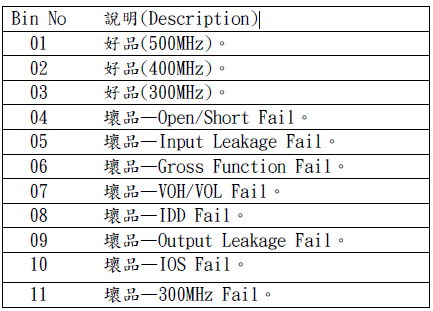

依測試結果所作的分類,英文稱為Binning。一般口頭上會說「分Bin」。測試程式在規劃之初,會有「Bin別定義的安排」。例如:好品歸類為Bin 1。壞品歸類為Bin 4等。當然Bin別定義不會如此簡單。每一個Device,會有自己一套Bin別定義。Bin別定義在不同的公司裡,也各自有一套定義。下面這個表格,是一個分Bin的範例。

Bin對於測試程式開發人員,會有所謂的硬體Bin(Hard Bin)與軟體Bin(Soft Bin)之分。硬體Bin是Handler機台,所能分類擺放的空間。因為測試後,需要將實體,擺放在Handler的某一特定位置。此特定位置因Handler的設計,而有數量上的不同。因此Hard Bin的數量,是有限制的。而Soft Bin顧名思義,它是軟體上的分類,它的數量較無限制。它只會顯示在測試報告中,實體上不會依此分類。一般分類到200種Bin,是沒有問題的。相對於Hard Bin而言,可能最多可分類到10多種Bin,取決於Handler機台的限制。

測試項目的先後次序,決定了測試流程(Test Flow)。測試程式的開發品質,也與此流程息息相關。之前的章節曾經提到,某些直流參數測試。在量測前,需要作Precondition的動作。而一般Precondition的動作,皆以執行Pattern的方式來達成。因此,在這樣的前提下,如果功能參數測試無法Pass,則量測此參數就變得無意義了。

測試流程對量產測試的影響很大。所謂的量產測試,是Device已決定量產後的一道測試步驟。這裡要讓讀者明白的是,Device在開發而未決定量產前,也是需要測試程式來作驗證。而這段時間的驗證,測試程式比較注重在各種參數的量測及其數據的收集。一般比較不會顧慮測試時間的長短。而且比較重視是否透過測試程式,能否收集到更多的數據。再依這些測試結果,作各種失效分析及製程改善。

而量產程式需要考慮的有(1)利用最短的時間,將好壞品區分出來。(2)最短的時間,區分出最多的Bin。(3)最短的時間內,收集最多參數值。在這樣的要求下,正考驗著測試程式開發人員。通常測試流程,會因不同的時間,及不同因素而改變。時常會因為要減少總測試時間,而將某些測試項目刪除。當然也有因為製程良率提昇後,而減少某些測試項目。

一般提供測試服務的國內封測廠,以所謂的Hourly Rate來做收費的計價標準。而Hourly Rate,就是依不同測試機台的成本,及其它相關費用所換算出來的費率。此費率以小時計算。有些測試機台,動則上億台幣成本。換算後的Hourly Rate,仍相當可觀。在這樣的前提下,減少測試時間,可以用來降低整體製造成本。

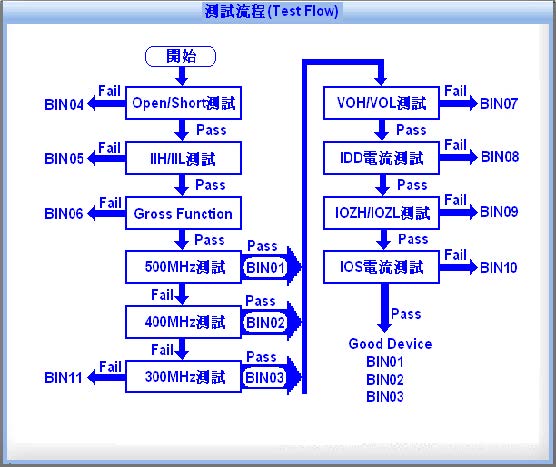

圖1。是測試流程(Test Flow)的一個範例。這裡再提一個程式流程(Program Flow)的觀念。筆者希望將測試流程與程式流程區分開來。主要的區別是,測試流程只是針對測試項目,作先後次序的安排,及分Bin方法與條件的定義。程式流程,它包括測試流程及其它測試硬體與設備相關的運作流程。舉一個較簡單的例子:在CP測試的階段。在測試前,將Wafer上面的雷射編碼(Laser Mark),讀入測試程式後,才開始測試。這樣的流程,定義為程式流程(Program Flow)。這些程式流程,不會在這裡提到太多。實務上並不困難。只要有機會,讀者應能瞭解。

因此,要瞭解一顆Device的測試結果。首要的工作,是先知道Device的測試流程(Test Flow)。如果您是產品工程師或製程工程師,測試程式不是您主要的工作內容時,您可著重於測試流程。而程式流程,就留給測試開發人員去處理罷。

圖 1 測試流程(Test Flow)

輸入腳漏電流量測(IIH/IIL)

輸入腳在邏輯1時的漏電流量稱為Input Leakage in High簡稱IIH。輸入腳在邏輯0時的漏電流量稱為Input Leakage in Low簡稱IIL。從這個章節開始,各位讀者應該有能力瞭解及認識這些參數的簡稱,往後的篇幅就盡量以簡稱來描述。

數位IC的規格表,通常會有以下的描述。

| Symbol | Description | Test Condition | Min | Max | Unit |

| IIH/IIL | Input Current | VDDmax=5.25V | -10 | +10 | μA |

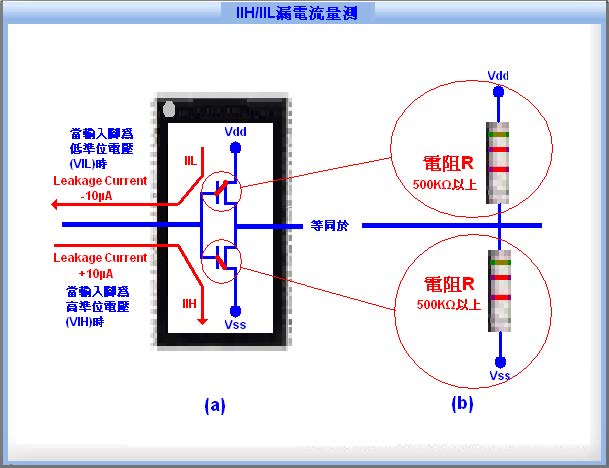

IIH的量測條件是,VDDmax=5.25V,而待測腳要供應一個VIH電壓,讓待測腳處於邏輯1的情況,所量得的漏電流量,其值不可大於10μA。IIL的量測條件是,VDDmax=5.25V,而待測腳要供應一個VIL電壓,讓待測腳處於邏輯0的情況,此時所量得的漏電流量,其值不可小於-10μA。由圖5-2(a)來說明IIH 及IIL漏電流的關係。IIH漏電流是介於輸入腳到Vss 之間的電流量,它是流向Device的方向。IIL漏電流是介於Vdd到輸入腳之間的電流量,它是流出Device的方向。

輸入腳在正常操作下,會被驅動為邏輯1或邏輯0的準位電壓。而此時不希望在輸入腳上有電流的產生。如果有電流產生時,我們稱呼它為漏電流。再從另一個等效電阻的觀點來看,如圖5-2(b)。Vdd與輸入腳之間如同有一個等效電阻。而輸入腳與Vss之間也有一個等效電阻。當然我們希望,這兩個等效電阻值,趨於無窮大。如此,才不會有漏電流的產生。各位要瞭解,在電路的設計上,我們不希望輸入腳有電流的產生。

圖2

- 量測的原理

其實IIH/IIL的量測原理很簡單。就是供應一個電壓到待測物的輸入腳上。然後,利用電流計量測待測腳的電流量。IIH/IIL兩者是分開來量測的,也就是程式要寫成兩段。一段是IIH測試,一段是IIL測試。有的時候,因Device的特性,輸入腳設計上,會有其電性上的特殊性。因此其Pass/Fail的判斷標準值也會不一樣。此狀況下,需要將不同判斷條件的輸入腳,分成不同的Pin Group,再分別測試。IIH/IIL有三種測試方式,以下逐一說明:

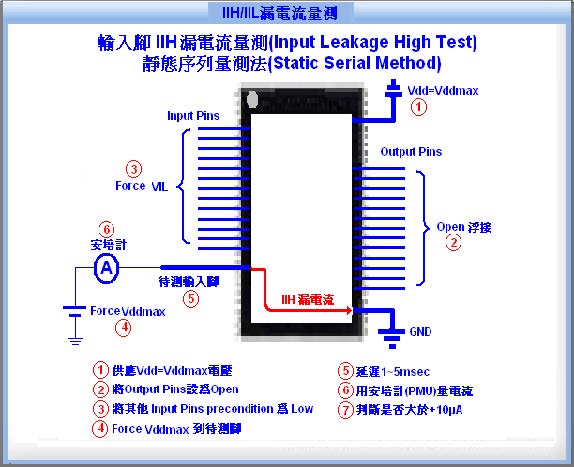

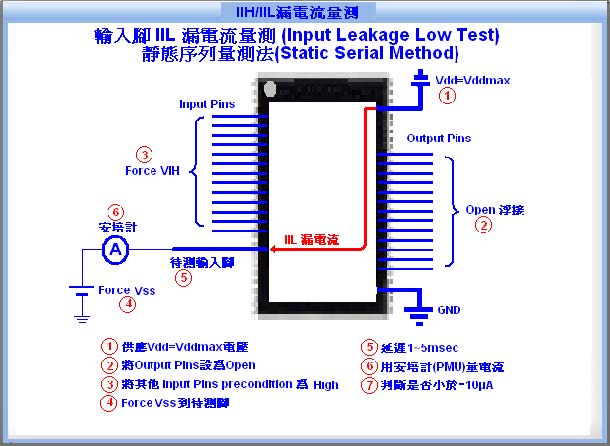

- 靜態序列量測法(Static Serial Method):

靜態(Static)一詞,在半導體測試工程領域裡,就是所有的輸入腳,從開始供應邏輯準位電壓,到量測結束的這段過程中,輸入腳的邏輯準位電壓都不會被改變。序列(Serial)一詞,就是依次序的,一個一個來量測的意思。所以靜態序列量測法(Static Serial Method),就是供應固定的邏輯準位電壓到每一個輸入腳後,再依序地量測每一支輸入腳的電流值。

圖3 輸入腳IIH漏電流量測(Input Leakage High Test)

靜態序列量測法,強調的是待測腳,依序逐一的使用PMU來量測。所有的輸出腳皆設為Open。其主要目的,是讓輸出腳無法產生電流。如此一來,再判斷輸入腳是否有電流。輸出腳可以設為Open,但輸入腳千萬不要設為Open。否則會有CMOS Device的Latch_Up現象。對於某些Device而言,不適合同時設定所有輸入腳為Low或High。這時候可用另一種解決辦法,就是獨立的量測每一支腳。首先,供應一個低電位(Low Level)到待測腳後量電流,再接著供應一個高電壓(High Level)到待測腳後再量電流。待測腳需要回到原來的邏輯準位電壓後,才可以接著測試下一支輸入腳。

請注意Device的功能表中,當所有的輸入腳為High Level或Low Level時,是否因此產生錯誤的Precondition條件。對於雙向腳(Bi-Directional Pin)而言,尤其重要。例如,當您在測試IIH/IIL時,如果,因為同時將輸入腳High或Low,而導致雙向腳變為輸出腳,這時候的量測可能就失去意義。如果這些接腳的電壓,是由測試機台所驅動時,較高的IDD電流,會導致Device內部的電源供應電壓,下降到輸入腳準位電壓之下。這樣的結果,會引起輸入腳的保護電路吸入電流。

如果Device是CMOS電路,雙向腳為Floating的情況時,也會有高電流的情況發生。一般的邏輯Device不希望有高電流的產生。除了耗電的理由外,高電流會破壞Device本身或以外的電路或設備。要解決這樣的問題,有一種辦法是,在雙向腳上連接一個輸出負載。將雙向腳電位,很確實地Pull到High Level或Low level。這樣一來,在測試的過程當中,不小心發生以上現象時,電流會被輸出負載所限制。還有一點,這裡所介紹的IIH/IIL量測,一般只針對純輸入腳(Only Pure Input Pins)而言。

圖4 輸入腳IIL漏電流量測(Input Leakage Low Test)

靜態序列量測法的優點是:一、它可以量測每一支輸入腳的單獨漏電流。二、它是屬Pin to Pin 的漏電流量測。三、待測腳在這樣的量測方法下,會接收來自所有輸入腳的不同電壓。因此,任何可能產生漏電流的管道,皆可被發現。但它的缺點是,比較耗費時間。

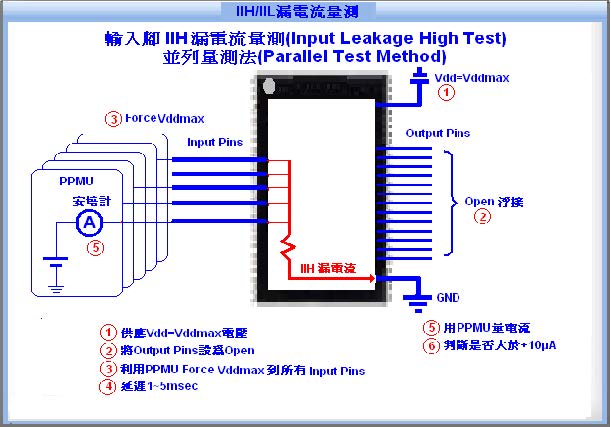

- 並列量測法(Parallel Test Method) :

圖5 輸入腳IIH漏電流量測(Input Leakage High Test)

使用並列量測法的前提是,測試機台需要具備並列量測所需的硬體結構。例如PPMU的設計。由圖5可知,每一個PPMU,同時供應Vddmax電壓(量IIH時)到所有輸入腳。它與靜態序列量測法不同。讀者可仔細比較它們之間的差異。並列量測法的優點是速度快。但缺點是無法得到所有輸入腳之間Pin to Pin的漏電流值。

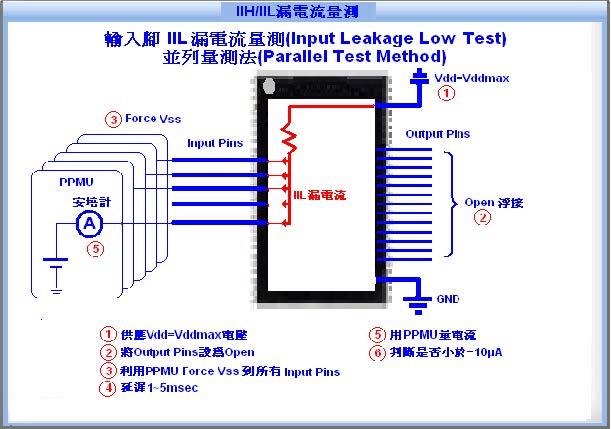

圖6 輸入腳IIL漏電流量測(Input Leakage Low Test)

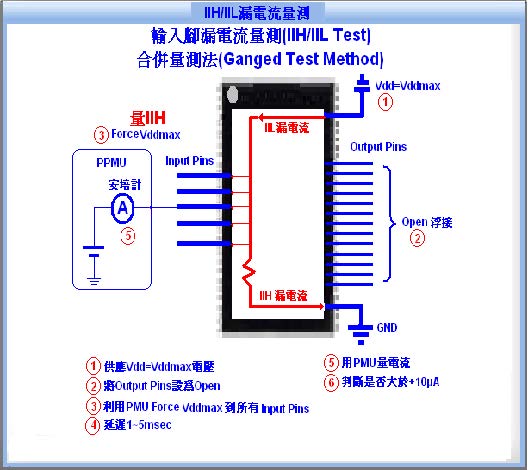

- 合併量測法(Ganged Test Method):

圖7 輸入腳漏電流量測(IIH/IIL Test) 合併量測法

合併量測法主要的差異,在於PMU供應準位電壓的方法。它只利用一組PMU,供應準位電壓到所有的輸入腳上。它只供應一次電壓準位到所有輸入腳,並只做一次的IIH或IIL的量測。然後根據量測到的電流值,作Pass/Fail的判斷。測試條件可依Device 規格表中的內容來設定。一般規格表中,會提供單一輸入腳的漏電流值。但合併量測法,所量到的值,是所有輸入腳的總合值。因此量到的值,如果超過條件值時,通常需要再用靜態序列量測法測量重新一遍。

為何需要合併量測法?它的優點是:速度快、不需要較昂貴的PPMU單元。缺點是,它無法得知那一支腳產生漏電流。但它對於具備高輸入阻抗的CMOS電路而言,是一種很有效率的測量方法。典型的CMOS電路,在正常的情況下,其輸入腳的總合漏電流量,會驅近於零。特別注意的是,此方法不適用於具備電阻特性的輸入腳,或具備Pull-Up或Pull-Down的輸入腳。因為這些輸入腳,通常所量到的電流量,一定會超過規格書中定義的漏電流量。

輸出腳高阻抗漏電流量測(IOZ)

前面一節介紹的是,輸入腳的漏電流參數。當雙向腳,被驅動為輸入腳的情況下,可用前一章節的方式,來量測漏電流。讀者稍微注意一下,如果要讓雙向腳變成輸入腳時,需要作Precondition的動作。本節將說明,輸出腳在Tri-State 狀況下,漏電流參數的量測,也稱為Output High Impedance Leakage Current。Tri-State/Z-State 也有人稱為High Impedance。而IOZH是雙向腳在由邏輯1時,被驅動為Tri-State(OFF) 狀況下的最大漏電流量(Output High Impedance Leakage Current High)。IOZL是雙向腳在由邏輯0時,被驅動為Tri-State(OFF) 狀況下的最大漏電流量(Output High Impedance Leakage Current Low)。

IOZ參數的規格表:

| Symbol | Description | Test Condition | Min | Max | Unit |

| IOZ | Output Current(High Z) | Vss≦Vout≦Vdd, Outputs Disabled | -10 | 10 | μA |

要量測輸出腳在High Impedance狀況下的漏電流量,首先要將輸出腳關掉(off)或稱Drive to High Impedance。 這個動作需要作Precondition,也就是執行一小段的測試向量。測試條件中的Outputs Disabled就是這個意思。而Vss≦Vout≦Vdd的意思是,輸出腳在邏輯1時,供應的電壓值(Vout=Vdd),而一般此時的Vdd=Vddmax。輸出腳在邏輯0時,供應的電壓值(Vout=Vss=0V)。兩者所量到的漏電流量,不可大於10μA或小於-10μA。這段說明前一章節已經提過,這裡重複的目的,的是省去翻頁的麻煩。

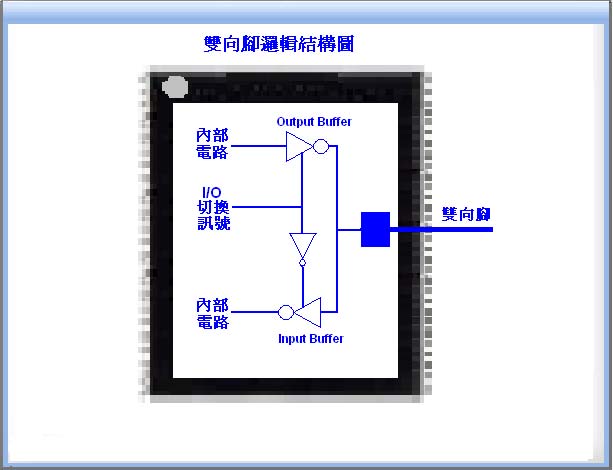

圖 A 用來說明雙向腳的邏輯結構圖。

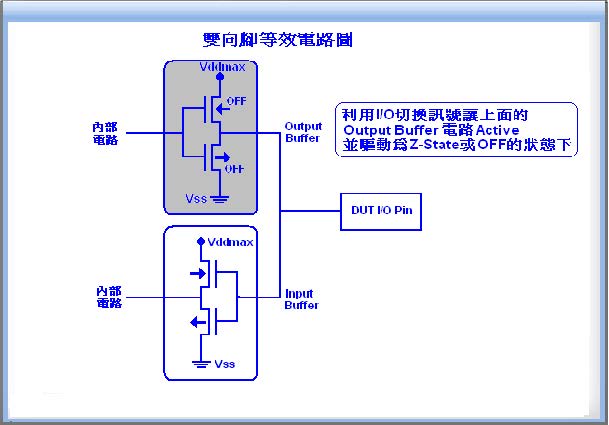

圖 B 雙向腳等效電路圖。

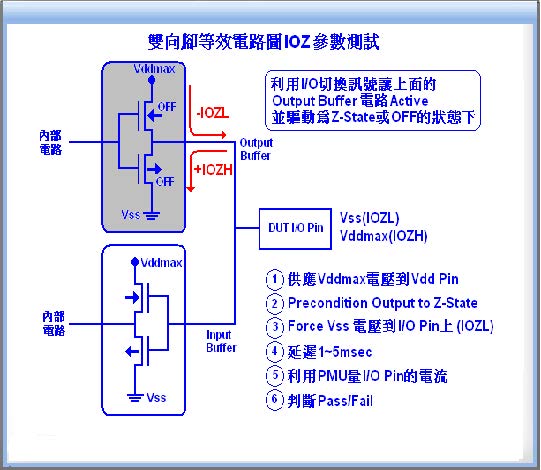

圖 C 雙向腳在IOZ測試時的等效電路。

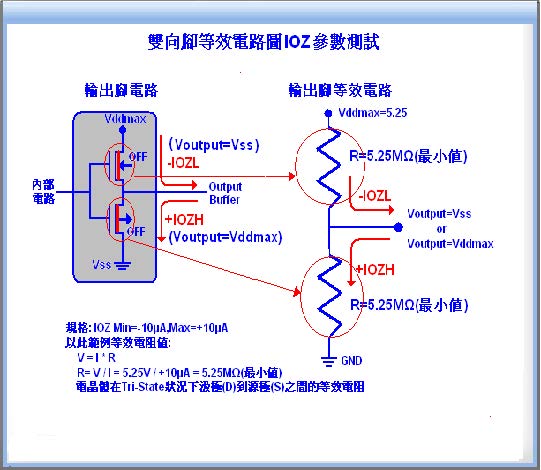

圖 D 雙向腳IOZ參數測試方式。

IOZ參數測試的主要目的是,雙向腳在OFF(Tri-State)的狀況下,是否能達到具備高阻抗的特性。如圖5-8d所描述的狀況。一般希望在此狀況下,電晶體的汲極與源極間的電阻值極大化,如圖例至少5.25MΩ。正常情況下,應該要量到趨近於零的漏電流。量IOZL參數,就如同量Vdd到輸出腳之間的等效電阻。量IOZH參數,就如同量輸出腳到Vss之間的等效電阻。此方法對於CMOS Device電路而言,是一種不錯的量測方式。IOZH/IOZL參數測試,有下列幾種測試方法:

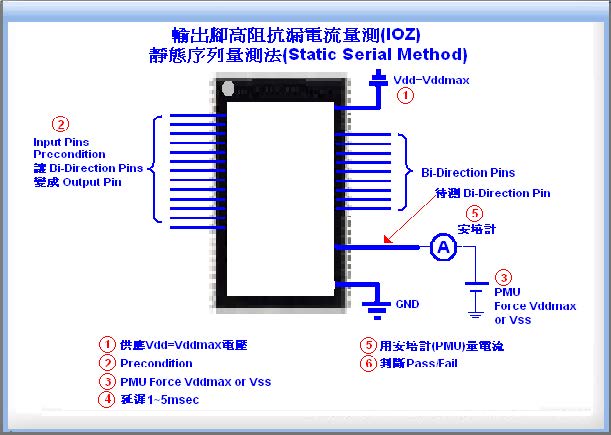

- 靜態序列量測法(Static Serial Method):

前面IIH/IIL參數量測,也曾經提到此方法。相同地,IOZH/IOZL參數量測時,大致相同。首先,供應一個電源電壓(Vddmax)到Vdd接腳,由輸入腳執行一段測試向量,讓雙向腳變成輸出腳。再利用PMU驅動一個電壓。如果要量IOZH時,則驅動電壓值為Vddmax。如果要量IOZL時,則驅動電壓值為Vss。等待約1~5msec

後,利用PMU單元量測電流。最後再做Pass或Fail的判斷。靜態序列量測法,強調的是每次量測,是一支腳接著一支腳量。其優點為可得到每支腳的電流值。其缺點是需要較多的量測時間。

圖9為IOZH/IOZL參數靜態序列量測法:

- 並列量測法(Parallel Test Method):

要使用並列量測法,一般測試機需要具備PPMU的硬體配備。此方法強調的是,同一個時間點可以針對,雙向腳做量測的動作,並取得每一支雙向腳的電流值。當然,這樣的量測方法,其成本相對地會比較高。此法的優點,當然是比靜態序列量測法快,缺點是比較貴。

圖10為IOZH/IOZL參數並列量測法:

耗電流量測(IDD)

IDD電流的意思是,CMOS電路的耗電流量。也就是由汲極(D極)到汲極(D極)的電流量。如果Device是屬於TTL電路的話,則稱為ICC電流。也就是由集極(C極)到集極(C極)的電流量。目前,因為CMOS電路在IC設計上,較廣泛被使用。實務上,大家會直接稱呼,IDD電流量測。如果您的Device是TTL電路時,請改稱呼它為ICC耗電流量測。此章節,皆以IDD電流稱呼。它是由汲極(D極)到汲極(D極)的電流量,所以量測的位置是Device的電源腳(Power Pin)。耗電流對Device而言,它代表的意義是,當耗電流越高時,Device消耗的電能越多。可想而知,耗電量越大,對使用成本及節約能源或環保的觀念來說,是IC設計者盡量避免的事情。

一般IDD電流,會在三種情況下來量測:一、較寬鬆的操作條件,這種條件下所量到的IDD電流,英文稱為Gross IDD。中文不好翻譯,就以英文直接稱呼。在業界,對Gross IDD電流的量測,沒有實質上的意義,所以大部份皆未作此部份的測試。但因環保因素,目前IC設計上,會有省電模式的設計。因此,會比較注重在各種省電模式下,IDD耗電流的量測。二、靜態的操作條件。靜態一詞,就是提供一組固定的測試向量來操作Device。在這樣的狀況下,所量得的電流,稱為靜態耗電流量測(Static IDD)。三、動態的操作條件,也就是讓電晶體在比較頻繁的情況下,做開關切換的動作,稱為動態耗電流量測(Dynamic IDD)。量測Dynamic IDD是希望知道,Device的最大耗電量的多寡。以下,會針對這三種IDD耗電流,逐一說明其量測的方法與步驟:

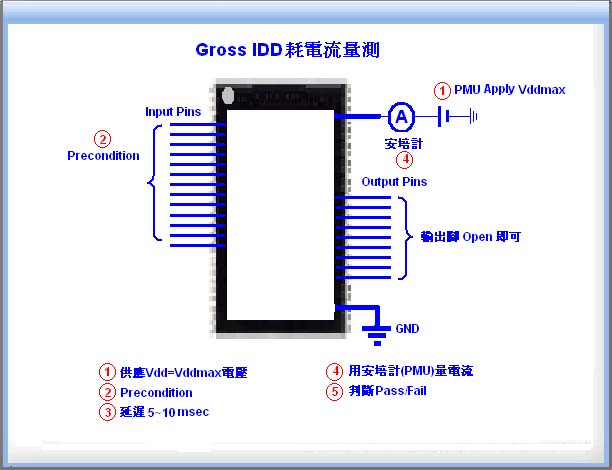

- Gross IDD參數量測

一般Gross IDD參數量測,是希望很快的知道,並且決定是否讓Device繼續往下測試的一個判斷參考。一般情況,測試流程的第一個測試項目,是Open/Short測試。讀者如果還有印象的話,您應該知道Open/Short測試時,Power Pin供應的電壓為Vss或零伏特電壓。此時未正式提供電壓給Device來操作。接下來的測試項目,需要正式的提供一個電源電壓到Vdd接腳(Power Pin)上。如果,這個時候,Device本身已經毀損,或有其它不良狀況,可能會引起不可知的狀況。有時候,甚至於會將Device及測試設備一併燒毀。因此,設計一道Gross IDD測試項目,來防止Device第一次通電後,可能會遇到不可知的狀況。

通常Gross IDD測試,會在CP測試或FT測試中被加入。它通常會在須要執行測試向量的測試項目之前來量測。如果Device能很正常且順利地執行Precondition的動作時,通常會省略它。量測Gross IDD電流,需要正確的Precondition測試向量。量測時,請詳閱IC規格表中,對IDD電流的定義。IC規格表中,通常不會保證這個時候的IDD電流值的條件限制。但可以知道的是,測試條件,一定要比較寬鬆。

Gross IDD的Precondition測試向量,一般會將所有的輸入腳,同時設為高電位、或同時設為低電位、或者Device如果有Reset的輸入腳功能時,可輸入一個Reset訊號給Device,以達到Precondition的目的。一般情況下,輸入腳的VIL=0V而VIH=Vdd,輸出腳不需要加掛輸出電流負載。如果加掛輸出電流負載時,會增加IDD的電流量。這樣的測試結果並不正確。Precondition 測試向量如何才正確?其實沒有定論,完全依Device的功能來決定。但一個原則是,這樣的Precondition 測試向量要盡可能地簡單化。接下來,才在電源腳上量測IDD電流,最後判斷是Pass還是Fail。一般如果是Fail的話,這個DUT就不再往下測試其它的參數。

比較傷腦筋的是,如何決定Gross IDD的判斷條件呢?通常需要取幾個不同的Device樣品,量測並觀察所量得的結果,再做最後的決定。通常會經過兩三次的修改後,才會最後確定。

圖11Gross IDD參數量測示意圖。

- Gross IDD參數量測步驟:

(1) 使用DPS或PMU單元,供應VDDmax電壓到Vdd腳。

(2) 設定最大限流(Current Clamp)。

(3) 設定Pass/Fail條件值。

(4) 設定Precondition測試向量並執行。

(5) 停止測試向量。

(6) 延遲5~10msec。

(7) 使用PMU單元,量測Vdd腳上的IDD電流。

(8) 判斷Pass或Fail。

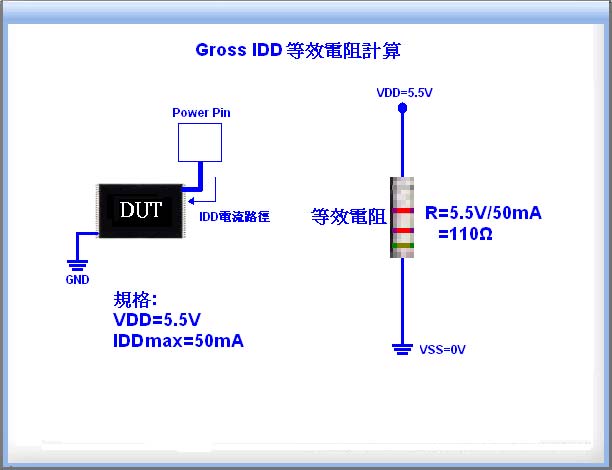

圖12Gross IDD等效電阻計算。

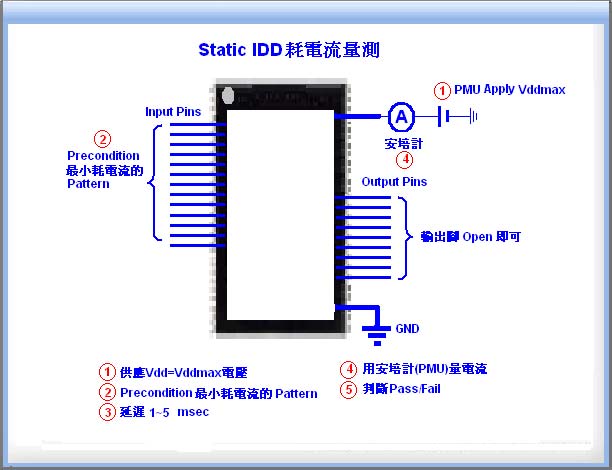

- Static IDD參數量測

Static IDD是在靜態的操作條件下,所量到的耗電流量。一般會希望量到,Device的最小耗電量。如果Device有設計省電模式時,Static IDD就是省電模式下的最小耗電量。這個參數的量測,對於使用電池裝置的設備而言,是相當重要的一項測試。下面這個表格為IDD Static電流參數規格表的範例。

| Symbol | Description | Test Condition | Min | Typ | Max | Unit |

| IDD Static | Power Supply Current | VDDmaxVdd=5.5V | – | 15 | 20 | mA |

此規格表的測試條件,供應電壓Vdd=5.5V。其IDD Static電流量不可大於20mA。其測試方法與前面的Gross IDD參數,大致相同。最大的差異在Precondition測試向量。這個測試向量的主要目的,是讓Device進入最小耗電量的狀態之下,並維持此狀態直到Static IDD電流量測結束為止。通常在量測此參數時,會影響此參數的原因,有以下幾項因素。例如: VIH、VIL、VDD、Test Pattern、及輸出負載等因素。當然,這個測試向量,IC設計者會提供最正確的Pattern以便測試。如果無法提供時,必須藉由實驗的方式,來取得此一Pattern。Pattern的正確性,決定了是否能量測到此一Static IDD耗電流。

測試時要特別注意到,如果規格表中的Static IDD條件,是一個很小的電流量時,請在量測前增加一點延遲時間(Delay Time/Settling Time)。 一般的測試設備,尤其在Probe Card製作時,測試Channel到Power Pin之間會加焊一個By-Pass電容,此電容是防止低頻雜訊的干擾。這樣的情況下,會影響到Static IDD參數的量測。某些狀況下,必需稍加修改一下Probe Card並加裝一些繼電器(Relay),在量測的過程中,利用Relay將By-Pass電容斷接(disconnect),再量測Static IDD參數。

- Static IDD參數量測步驟:

(1) 使用DPS或PMU單元,供應VDDmax電壓到Vdd腳。

(2) 設定Precondition Pattern並執行。

(3) 停止Pattern。

(4) 延遲1~5msec。

(5) 使用PMU單元,量測Vdd腳上的IDD電流。

(6) 判斷Pass或Fail。

圖13 Static IDD耗電流量測示意圖。

- Dynamic IDD參數量測

動態耗電流量測,是Device在動態的操作條件下,也就是讓電晶體開關切換比較頻繁的情況下,來量測耗電流量。重點還是在Precondition測試向量,如何達到此動態的條件。以下是一個範例,

| Symbol | Description | Test Condition | Min | Max | Unit |

| IDD Dynamic | Power Supply Current | Vdd=5.5V, f=fMax(100MHz) | – | 20 | mA |

這個範例,是說明在Dynamic IDD測試時的條件。電源電壓為5.5V,而操作頻率為100MHz。此時所量出來的耗電流量,不可大於20mA。Vdd = Vddmax = 5.5V。這個條件,是希望Device在最糟的情況,是否仍滿足規格的要求。一般Dynamic IDD的量測,是希望Device在頻繁的操作環境下,所量得的最大耗電量。與前面兩種IDD最大的不同,還是在於Precondition Pattern。其它量測時應配合或注意的事項大致相同。

通常在量測此參數時,會影響此參數的原因有以下幾項因素。例如: VIH、VIL、VDD、Test Pattern、及輸出負載等因素。特別注意,在供應電源電壓Vddmax時,有的測試機台可利用DPS或PMU兩種不同的單元來供應電壓。如果DPS對低電流量測的精密度不足時,可能就要改用PMU單元來量測。這個時候,會花較多的測試時間。

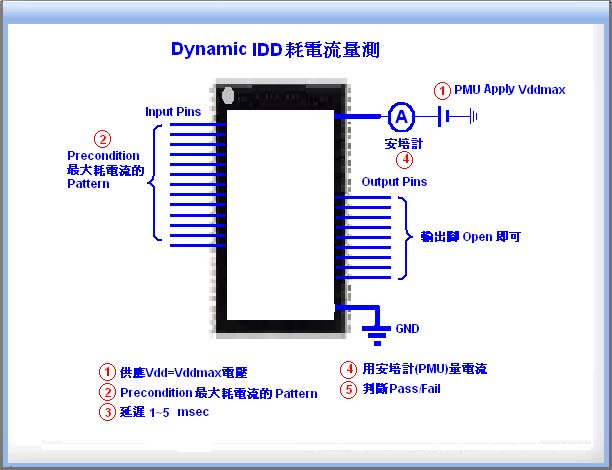

- Dynamic IDD參數量測步驟:

(1) 使用DPS或PMU單元,供應VDDmax電壓到Vdd腳。

(2) 設定Precondition Pattern並執行。

(3) 停止Pattern。

(4) 延遲1~5msec。

(5) 使用PMU單元,量測Vdd腳上的IDD電流。

(6) 判斷Pass或Fail。

圖14 Dynamic IDD耗電流量測示意圖。

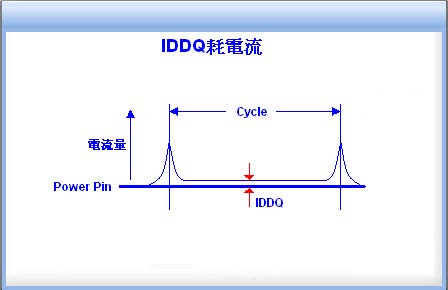

- IDDQ參數量測:

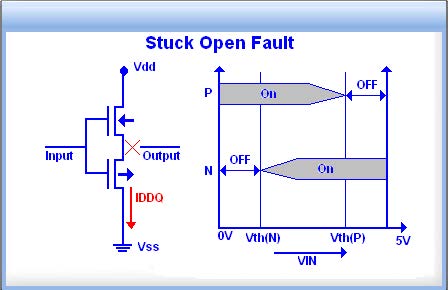

一般IDDQ電流的量測,是屬於比較高階的一種測試項目。在半導體測試工程入門的書籍裡,很少會詳細的探討。這裡,筆者也只作簡略的介紹。IDDQ這個名詞,很少有翻譯。其中Q是「暫態」的意思,大致上可以解釋成,「在某種特殊的條件下,所量得的IDD電流量」。一般狀況下,這個電流量是很微小的。在CMOS電路裡,利用IDDQ參數的量測,是很有效率的一種方法。它是一種簡單且簡便的方式,來找出Device的缺陷及不良。要找出IC在功能上的不良,一般直覺的想法是,利用執行Pattern的方式來檢測。但是Pattern可能須要上千行或者更多,才有辦法測試出IC是否正常。這個時候,或許可以考慮用IDDQ電流量測方式。

目前的Device,大多採用Cycle Base的操作模式。也就是,輸出腳與輸入腳的邏輯變化,是以周期為基準。如圖15所示,電源腳在每一個Cycle的前後,會有電流的消耗。而Cycle中間的電流消耗,是比較穩定且微小。這個微小電流量,屬μA級的電流,也就是這節所說的IDDQ電流。一般的PMU單元,無法量得此電流量。一般會藉用IV Converter (電流電壓轉換器)來量測。

圖15 IDDQ耗電流

故IDDQ的量測,需要特殊的硬體設備及特殊的設計。這裡所謂的特殊設計是,在IC設計階段時,就需要考量到測試的方法。因此IC設計公司,如果具備較多的IDDQ測試方法,則表示此設計公司的設計能力較強。相同地,測試機台的供應商。如果能提供更多的硬體設備,來量測IDDQ的話,其競爭力也就較強。

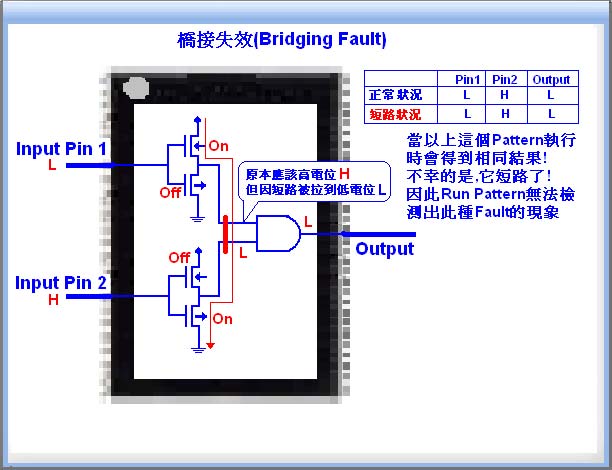

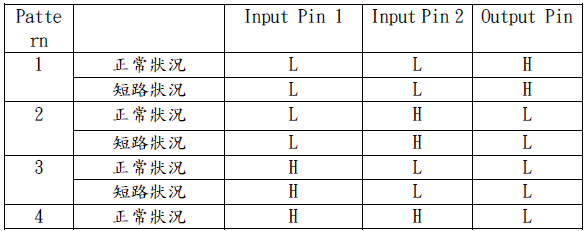

以下的介紹,是利用IDDQ電流量測方法,找出CMOS數位邏輯電路的三種Fault Model(IC失效模式)

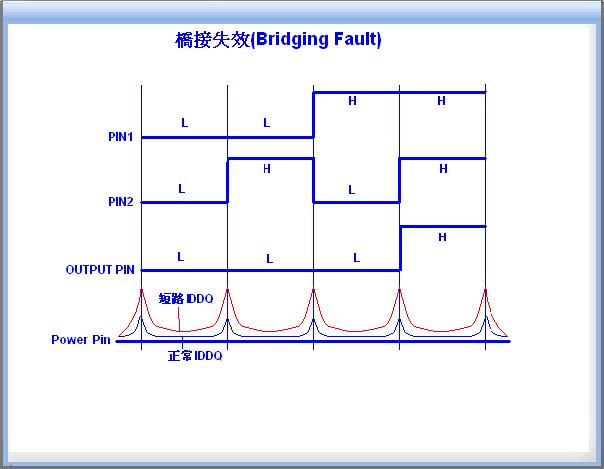

- 橋接失效(Bridging Fault):

圖16 是由上下兩個反向器電路及一個AND閘,所組合成的一顆IC電路。

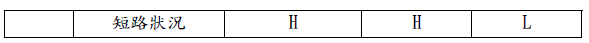

其真值表如下:

由以上的真值表的分析得知。當短路狀況發生時,執行Pattern時,根本無法檢測出此種失效模式。但我們可以藉由IDDQ電流的量測,得知它的異常。圖17為Pattern 1-4,Power Pin的IDDQ電流的可能變化示意圖。 這裡特別注意,當其中一個反向器輸出為低電位時,不管另一個反向器的輸出電位如何,皆會被拉回低電位。

圖17

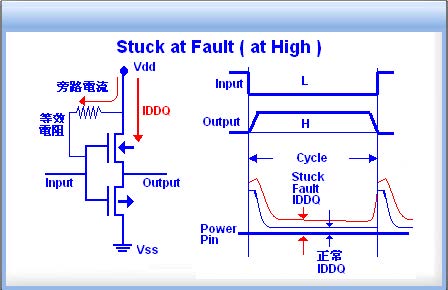

- Stuck at Fault:

Stuck at Fault有兩種,一種是at High、一種是at Low。也有人稱為Stuck at 1 或Stuck at 0。Stuck at High得意思,由字面的解釋,不管外在狀況的改變,它的電位一直停陷在高電位。Stuck at Low得意思,不管外在狀況的改變,它的電位一直陷於在低電位。圖18,是Stuck at High 的一個範例。以一個反向器來舉例,當輸入腳為High時,VDD到Input端之間沒有電流產生,與正常狀況下無異。

當輸入腳為Low時,VDD到Input端之間,產生旁路電流,並且使得IDDQ的電流量產生變化。特別注意,這個狀況下,反向器的功能仍然正常。意思是,當Input Pin在高電位時,Output Pin則在低電位。當Input Pin在低電位時,Output Pin則在高電位。仍滿足真值表的要求。但正常狀況下與Stuck at High的狀況下,這兩者的IDDQ電流量是不一樣的。因此,要找出此種Fault Model,使用IDDQ參數量測法是必要的。

圖18

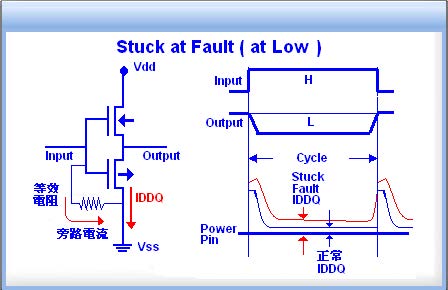

圖19,是Stuck at Low 的一個範例參考。其道理一樣,只是Input Pin為高電位時,Input Pin到VSS之間才會產生旁路電流。

- Stuck Open Fault:

圖20是Stuck Open Fault的一個範例。這個範例是內部實體電路中斷。因此輸出腳為Stuck Open的狀況。此範例顯示,上下兩個CMOS電路閘的電壓,會呈現不穩定的狀態。但IDDQ電流,仍會從VDD流向VSS。這個時候,無法量到IDDQ電流的變化。雖然沒有變化,並不表示沒有Fault在其中。

圖20

量測IDDQ電流,有以下幾個基本量測原則。找出以上所提到的Fault Model,並執行所需要的Pattern。再利用電壓電流轉換器量得IDDQ電流量。如果要求錯誤含概率要高一點的話,您可能須要較多的測試向量及測試時間。

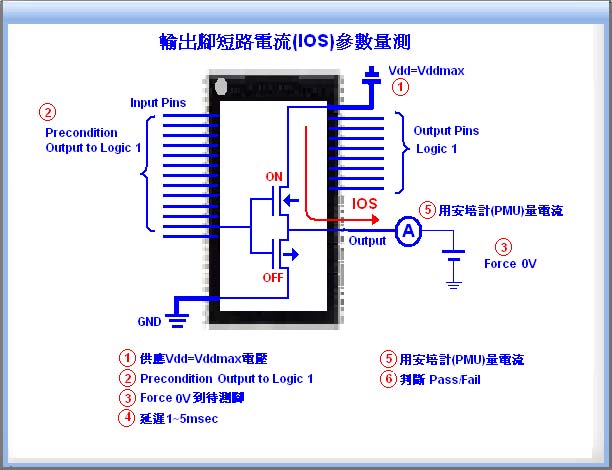

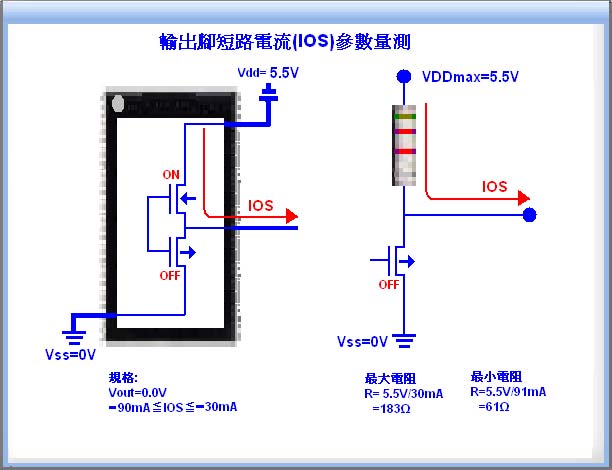

輸出腳短路電流量測(IOS)

輸出腳短路電流量測(Output Short Circuit Current)。讓輸出腳處於一種短路狀況下,所量得的電流。 以下是一個規格表範例:

| Symbol | Description | Test Condition | Min | Max | Unit |

| IOS | Output Short Circuit Current | Vout=0V,Vdd=5.0V, Short only one output at a time for no longer than 1 second | -90 | -30 | mA |

規格表中提到,當輸出腳被驅動為邏輯1時,供應一個Vout=0V的電壓到輸出腳上。特別注意的是,每次只能針對一支輸出腳這樣做。這個動作,在這裡稱為短路(Shorted)。接著利用PMU來量電流值。

這樣量測的目的,是希望輸出腳外接到外部電路時,如果遇到最壞的狀況下,還能保證提供規格表中,所定的等效輸出阻抗,並保證輸出腳的輸出電流量,如規格表中所定的最小電流量-90mA,而最大電流量為-30mA。這時,所量出來的電流量,也可以說是Device輸出腳可以供應下階電路的最大電流量。此電流量,可用來當作電容負載的電流量。並可用來計算,輸出腳的上昇時間(Rise Time)。

■ 輸出腳短路電流量測(IOS)—序列靜態量測法:

輸出腳短路電流序列靜態量測法,讀者應該相當熟悉這個名詞了。首先執行一段Precondition Pattern讓所有的輸出腳為邏輯1的電壓準位。然後利用PMU單元,供應一個0V的電位到輸出腳上。接著量測輸出腳的電流。每次只能針對一支輸出腳這樣做,直到所有的輸出腳皆被量測完畢。這種量法就稱為序列靜態量測法。IOS參數量測,只能用此方法。IOS參數的條件值,通常會有上限值與下限值的規定。請詳細閱讀規格表,對其測試條件及量測時的相關說明。尤其是短路的時間最大限度。如果時間過久,會對Device造成Overheating的現象。

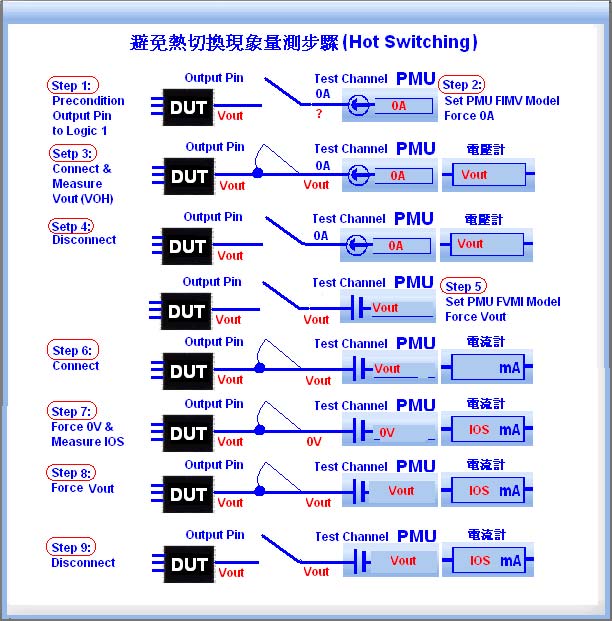

讀者應該會注意到,輸出腳被驅動為邏輯1的高電壓準位時,又再利用PMU供應一個0V的低準位電壓。此時輸出腳是高準位電壓,而PMU的測試Channel上是低準位電壓。這時候,如果讓一高一低的電壓連接,會產生所謂的熱切換現象(Hot Switching)。這樣的現象,會產生一個高電流。情況嚴重時,會燒毀DUT或

測試的硬體設備。

所以,在做此項參數量測時,需要避免熱切換現象(Hot Switching)的發生。如何避免熱切換現象呢? 簡單的一個觀念是,先讓兩端,形成等電壓的狀況,再將輸出腳與PMU的Test Channel連接在一起。為了要達到這個目的,首先要知道輸出腳的電壓值為何? 可以事先理解的是,它應該介於VDD與VOH之間的電壓值。這時候,先將PMU設定為供電流量電壓的模式(IFVM Model),供應零安培電流。然後將PMU的Test Channel與DUT的輸出腳連接,並量測VOH電壓。

將量測所得到的輸出腳VOH電壓值,記錄並儲存起來。這個時候,可以得到輸出腳的實際輸出腳電壓值(VOH)。取得後,將PMU與DUT斷接(Disconnect)。並將PMU改設定為供電壓量電流的模式(VFIM Model),供應剛才所量得的VOH電壓值。此時DUT與PMU Test Channel上,兩邊為相同等電位。這個時候,就可以將兩者連接在一起。接下來,由PMU轉為供應0V的電壓,並量測IOS電流值。記得要在斷接之前,PMU要改為剛才所量得的VOH電壓值。目前的測試機,都會有避免熱切換現象的機制。以下是量測步驟與示意圖21。

圖21 避免熱切換現象量測步驟

■ 輸出腳短路電流(IOS)參數量測步驟:

(1) 供應VDDMax電壓到DUT的Power Pin。

(2) 執行Precondition Pattern。這個Pattern需要能夠讓Output Pin變成邏輯 1的狀態。

(3) PMU設定好限流(Current Clamp)設定。

(4) 利用PMU供應0V電壓到單一的輸出腳上。

(5) 延遲1~5msec後,量測IOS電流。

(6) 判斷Pass/Fail。

Ps:測試步驟中,沒有提到如何避免熱切換現象。請向您的硬體供應商詢問,如何處理。

圖22輸出腳短路電流(IOS)量測示意圖。

圖23 IOS等效電阻計算示意圖

輸出腳電壓量測(VOH/IOH)

VOH(Output Voltage in High),輸出腳在邏輯1時的最小電壓值。IOH(Output Current in High),輸出腳在邏輯1時的電流值。以下是一個規格表範例:

| Symbol | Description | Test Condition | Min | Max | Unit |

| VOH | Output High Voltage | Vdd=4.5V,VIH=2V,VIL=0.8V ,IOH=-4.5mA | 2.4 | – | V |

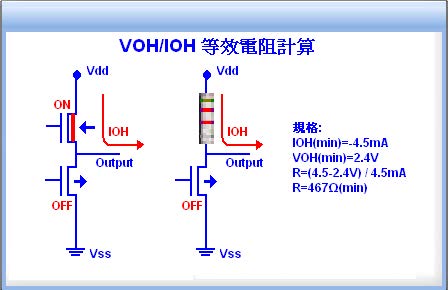

VOH/IOH參數測試的主要目的,是要確保輸出腳在邏輯1時,其輸出阻抗符合規格表中的定義。同時也確認IOH的電流值。圖24說明了,VOH/IOH參數測試,等效電阻計算。一般會希望此阻抗比,越小越好。

圖 24

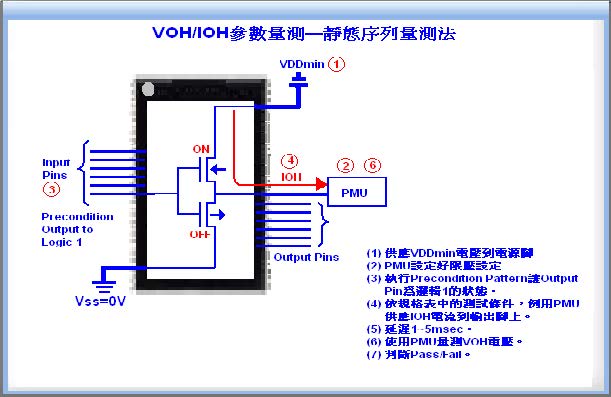

■VOH/IOH參數量測—靜態序列量測法:

量測VOH時,會有所謂的靜態VOH與動態VOH,這兩種參數的量測。這裡探討的是,靜態VOH參數的量測。首先要讓輸出腳形成邏輯1的狀態,必需先執行一段Precondition Pattern。再利用PMU供應一個電流(IOH),到輸出腳上。並量測此時輸出腳的電壓值。接下來判斷Pass/Fail。將所有的輸出腳,以此方式逐一的量測。這裡特別注意,Power Pin的電源電壓為VDDmin。這樣的作法,是希望以最壞的狀況下,所量得的輸出腳VOH參數,仍能滿足規格。IOH電流為一負向電流。測試時,記得要設定限壓設定(Voltage Clamp)。

■ VOH/IOH參數測試步驟:

(1) 供應VDDmin電壓到電源腳。

(2) PMU設定好限壓設定(Voltage Clamp)。

(3) 執行Precondition Pattern讓Output Pin為邏輯1的狀態。

(4) 依規格表中的測試條件,例用PMU供應IOH電流到輸出腳上。

(5) 延遲1~5msec。

(6) 使用PMU量測VOH電壓。

(7) 判斷Pass/Fail。

圖25 VOH/IOL參數測試步驟示意圖。

輸出腳電壓量測(VOL/IOL)

輸出腳在邏輯0時的最大電壓值。IOL(Output Current in Low),輸出腳在邏輯0時的電流值。以下是一個規格表範例:

| Symbol | Description | Test Condition | Min | Max | Unit |

| VOL | Output High Voltage | Vdd=4.5V,VIH=2V,VIL=0.2V, IOH=8mA | 0.5 | V |

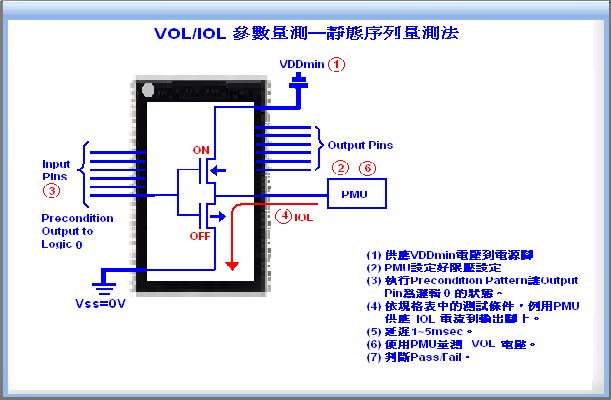

VOL/IOL參數測試的主要目的,是要確保輸出腳在邏輯0時,其輸出阻抗符合規格表中的定義。同時也確認,IOL的電流值。圖26說明,VOL/IOL參數測試,及等效電阻的計算。一般會希望此阻抗比,越小越好。

圖26

■VOL/IOL參數量測—靜態序列量測法:

量測VOL時,會有所謂的靜態VOL與動態VOL,這兩種參數的量測。這裡探討的是,靜態VOL參數的量測。首先,要讓輸出腳形成邏輯0的狀態,必需先執行一段Precondition Pattern。再利用PMU供應一個電流(IOL)到輸出腳上。並量測此時輸出腳的電壓值。接下來判斷Pass/Fail。將所有的輸出腳,以此方式逐一的量測。這裡特別注意,Power Pin的電源電壓為VDDmin。這樣的作法,是希望以最壞的狀況下,所量得的輸出腳VOL參數,仍能滿足規格。IOL電流為一正向電流。測試時,記得要設定限壓設定(Voltage Clamp)。

■ VOL/IOL參數測試步驟:

(1) 供應VDDmin電壓到電源腳。

(2) PMU設定好限壓設定(Voltage Clamp)。

(3) 執行Precondition Pattern讓Output Pin為邏輯0的狀態。

(4) 依規格表中的測試條件,例用PMU供應IOL電流到輸出腳上。

(5) 延遲1~5msec。

(6) 使用PMU量測VOL電壓。

(7) 判斷Pass/Fail。

圖27 VOL/IOL參數測試步驟示意圖。

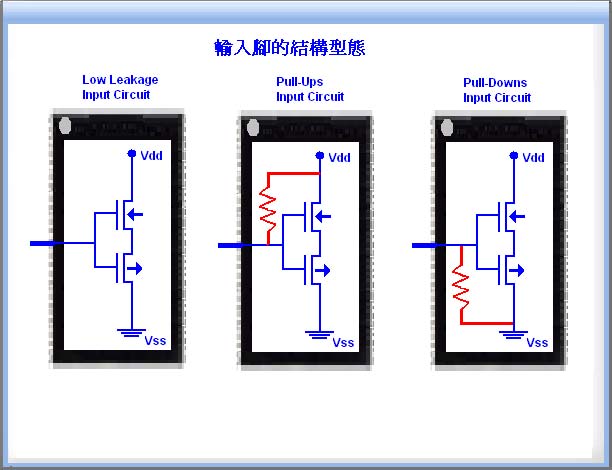

輸入阻抗(Resistive Inputs)

一般CMOS電路設計時,針對輸入腳會有以下三種型態的結構。不加阻抗迴路、拉高電位阻抗迴路(Pull-Ups)、拉低電位阻抗迴路(Pull-Downs)。圖28說明這三種輸入腳的結構示意圖。不加阻抗迴路這個結構,在前面的輸入腳漏電流量測時已有提到,其漏電流量應會很小,小到為零。也可以說,這個結構的輸入阻抗,非常的高。

其阻抗的量測方法,如同第二節輸入腳漏電流量測,所作的說明。拉高電位阻抗迴路(Pull-Ups),是由輸入腳到Vdd之間設計一個阻抗迴路。這個阻抗值,一般會比較小。並希望輸入腳,平時維持在高電位。拉低電位阻抗迴路(Pull-Downs) ,是由輸入腳到Vss之間設計一個阻抗迴路。相同地,這個阻抗值,一般也會比較小。並希望輸入腳,平時維持在低電位。特別注意俱備Pull-Ups及Pull-downs的輸入腳,其漏電流量會比較高。測試時,請特注意規格表中的說明。不要將一般的漏電流條件混在一起。

圖28

輸出驅動能力

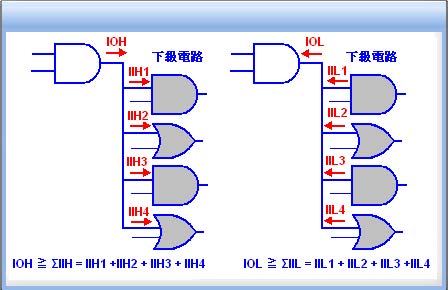

輸出驅動能力,英文為Output Fan Out。Fan Out也有人翻譯為扇出能力。任何的數位電路的輸出,都會連接下級的負載電路。如果連接的負載過大時,則電路會發生推不動的狀況。這些負載,可能是同類的數位電路。也有可能是異類的負載電路。當輸出為高電位時,次一級的輸入高電位電流總合,必需小於輸出高電位電流。IOH ≧ΣIIH。當輸出為低電位時,次一級的輸入低電位電流總合,必需小於輸出低電位電流。IOL ≧ΣIIL。 圖29為輸出驅動能力示意圖。

圖5-29

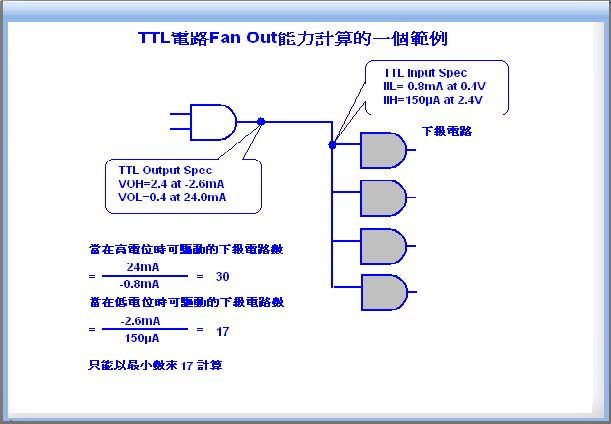

對應用工程師而言,他不但要知道應用上,其電壓及電流的需求,還要知道Device的每支輸出腳的輸出能力。這些訊息在規格表中,都應該被定義的很清楚。對測試工程師而言,必需依規格表中的條件作測試,並保證能達到規格。Fan Out對TTL電路及CMOS電路,是不太相似的。前面章節提到CMOS輸入腳,如果沒有Pull-Ups或Pull-Downs的設計時,其輸入阻抗是非常大的。並且其Input Leakage趨近於零。故理論上,CMOS電路的Fan Out能力,是無限的。意思是,可以連接無限個下級電路。而TTL電路的Fan Out能力,則是有限制的。圖30是TTL電路Fan Out能力,計算的一個範例。計算所需的參數,由以下的規格表提供。

| Symbol | Description | Test Condition | Min | Max | Unit |

| VOH | Output High Voltage | VCC=4.75V ,IOH=-2.6mA | 2.4V | V | |

| VOL | Output Low Voltage | VCC=4.75V IOL=24.0mA | 0.4V | V | |

| IIL | Input Low Load Current | Vin=0.4V | -800 | μA | |

| IIH | Input High Load Current | Vin=2.4V | 150 | μA |

圖30

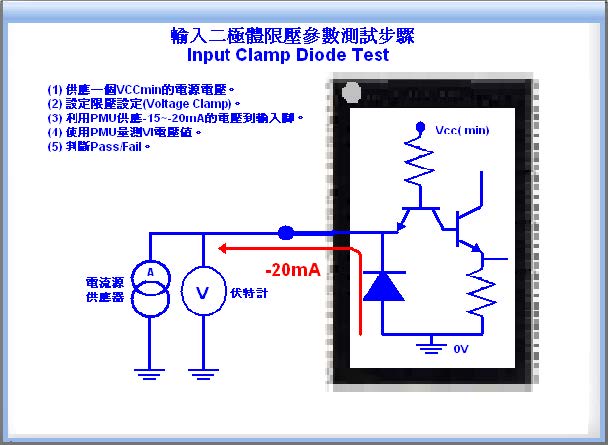

輸入二極體限壓參數

輸入二極體限壓參數,英文稱Input Clamp簡稱VI (Input Clamp Diode Test)。VI這個電壓值,只針對TTL電路而言。電路圖如圖5-31所示。其量測方式,從輸入腳Sink一個電流後,並量測輸入腳。這個時候的電壓值。圖中,電晶體的射極(Emitter)與Ground 之間,會有一個保護二極體(Diode)。這個二極體,是為了防止電晶體的射極(Emitter)電流流向Ground。因此要瞭解這個保護二極體(Diode),是否正常運作。可利用量VI參數來測試。以下是VI參數的規格範例。

| Symbol | Description | Test Condition | Min | Max | Unit |

| VI | Input Clamp Voltage | Vcc=min,Iin=-18mA | +1.5 | V |

圖31

■ 輸入二極體限壓參數測試—靜態序列量測法。

首先供應Vcc min的電壓到Power Pin。再利用PMU單元,從輸入腳Sink一個電流後,在輸入腳上量電壓。最後再作Pass/Fail的判斷。注意,VI參數,只能一支一支的量測。量測時,請注意要設定限壓設定(Voltage Clamp)。

■ 輸入二極體限壓參數測試步驟:

(1) 供應一個VCCmin的電源電壓。

(2) 設定限壓設定(Voltage Clamp)。

(3) 利用PMU供應-15~-20mA的電壓到輸入腳。

(4) 使用PMU量測VI電壓值。

(5) 判斷Pass/Fail。

PS:只針對TTL型態的Device作測試,CMOS型態不適用。