主頁

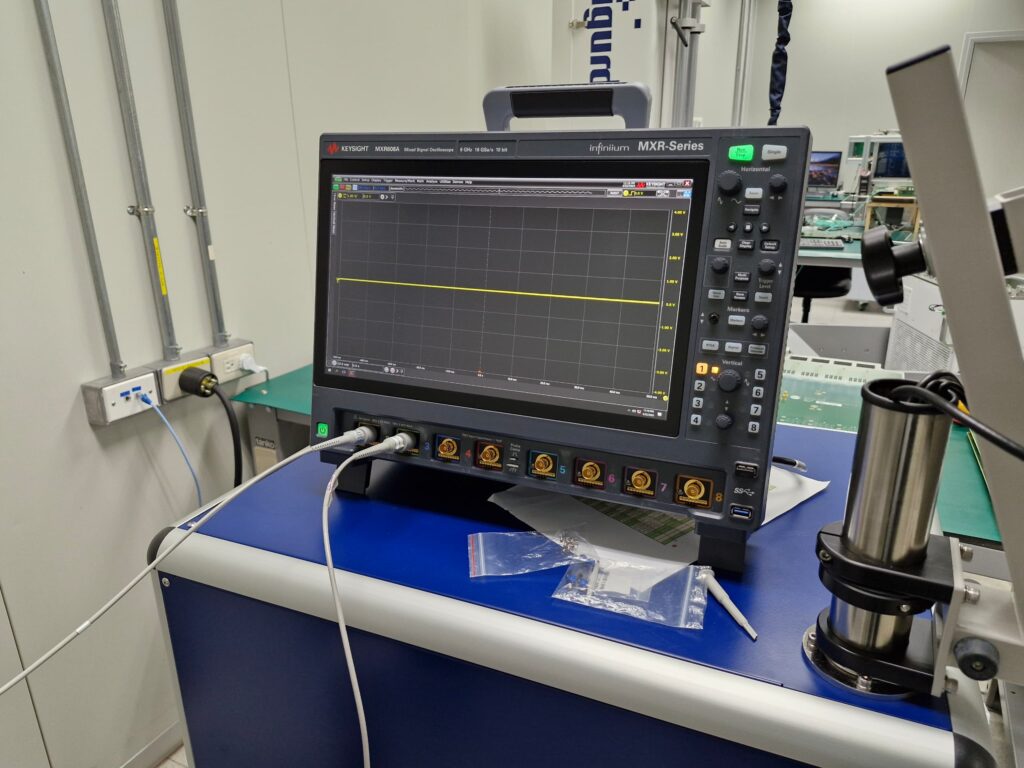

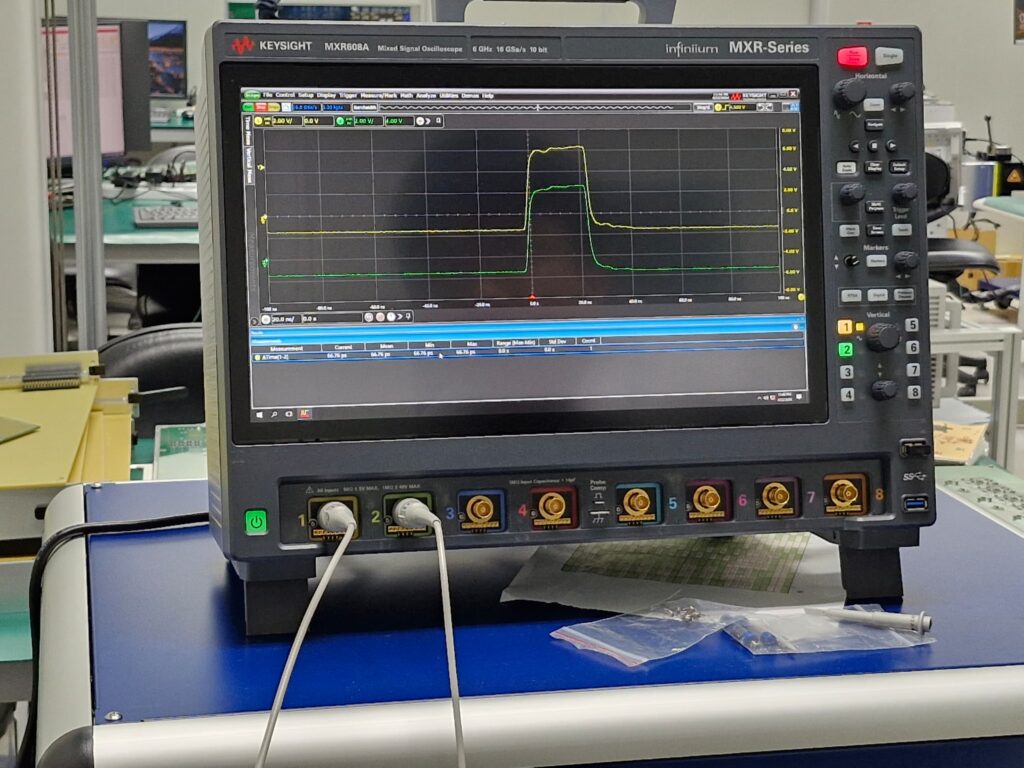

示波器

是一種能夠顯示電壓訊號動態波形的電子測量儀器。它能夠將時變的電壓訊號,轉換為時間域上的曲綫,原來不可見的電氣訊號,就此轉換為在二維平面上直觀可見光訊號,因此能夠分析電氣訊號的時域性質。更進階的示波器,甚至能夠對輸入的時間訊號,進行頻譜分析,反映輸入訊號的頻域特性。

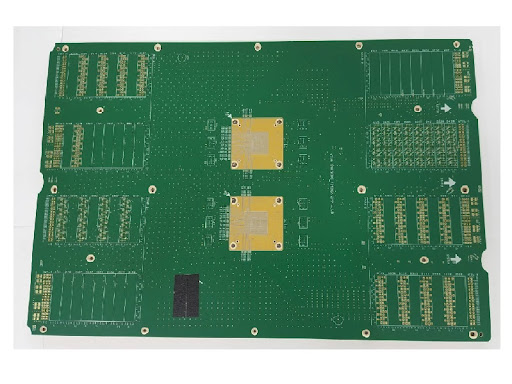

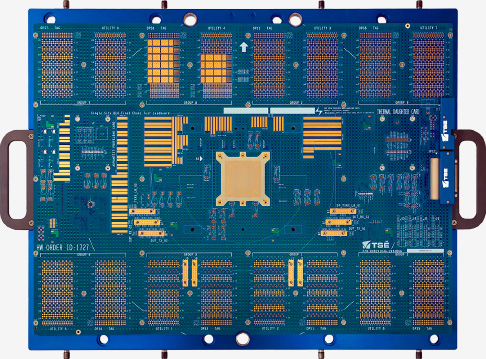

loadboard 測試載板

Load Board 是一塊高度客製化的PCB,做為IC 與自動測試設備ATE (Automatic Test Equipment)之間的傳輸媒介。隨著積體電路(IC)設計日漸複雜,在測試及驗證IC所花費的工夫也越來越多,對於Load Board 的設計及品質要求也日益漸高。

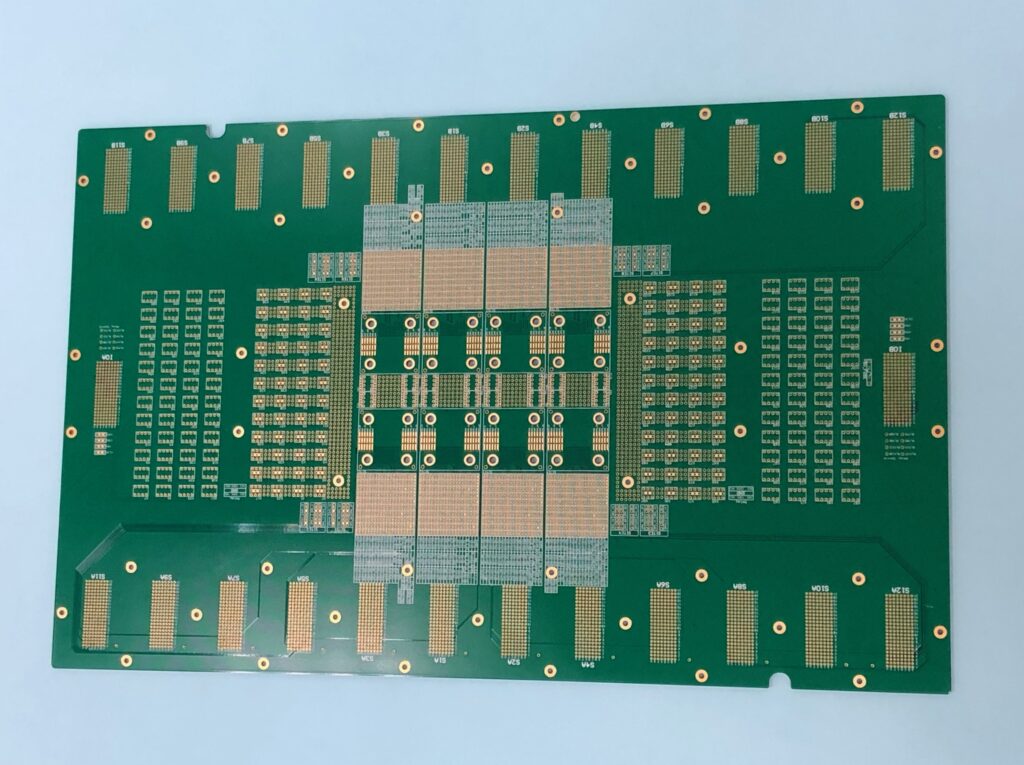

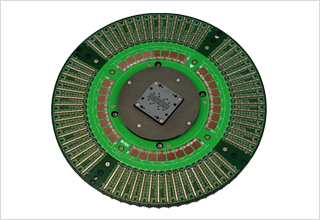

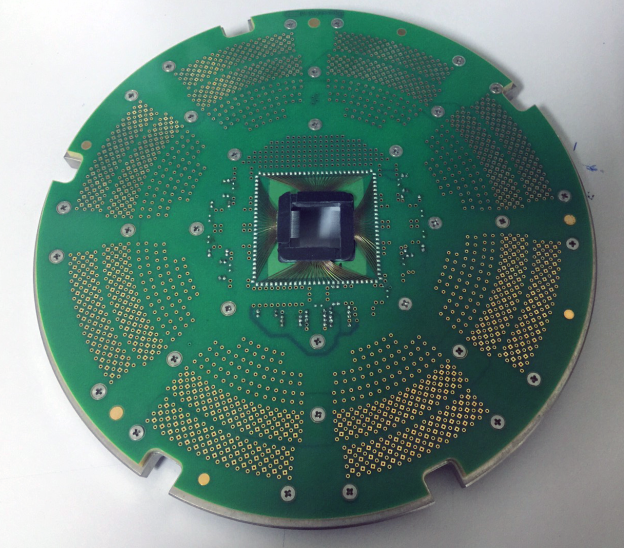

Probe card 探針卡

Probe card 探針卡是晶圓與電子測試系統之間。探針卡通常直接放在探測器上並用接線連接測試機。它的目的是提供晶片與測試機之間的連結,並完成並完成晶圓測試。通常包印刷電路板和其他要件,這種要件可能是金屬或其他材料。

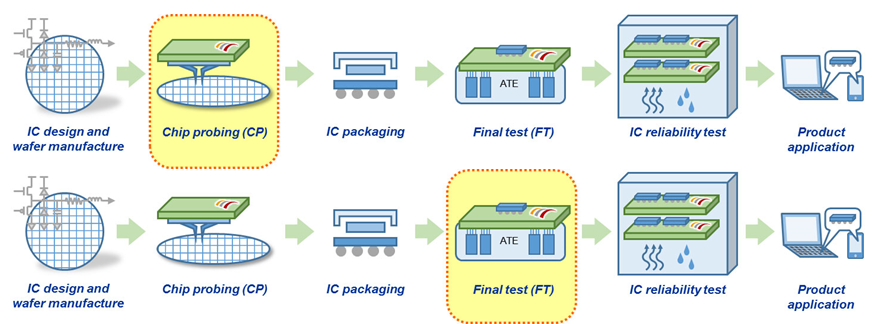

如何區分CP測試和FT測試

CP是(Chip Probe)的縮寫,指的是晶片在wafer的階段,就通過探針卡扎到晶片管腳上對晶片進行效能及功能測試,有時候這道工序也被稱作WS(Wafer Sort)。

FT是Final Test的縮寫,指的是晶片在封裝完成以後進行的最終測試,只有通過測試的晶片才會被出貨。

首先,CP最大的目的就是确保在芯片封装前,尽可能地把坏的芯片筛选出来以节约封装费用。所以基于这个认识,在CP测试阶段,尽可能只选择那些对良率影响较大的测试项目,一些测试难度大,成本高但fail率不高的测试项目,完全可以放到FT阶段再测试。

这些项目在CP阶段测试意义不大,只会增加测试的成本。要知道,增加一个复杂的高速或高精度模拟测试,不仅仅会增加治具的成本,还会增加测试机台的费率和增加测试时间。这些测试项目在FT阶段都是要测试的,所以没有必要放在CP阶段重复进行了。

其次,一些芯片的部分模组地管脚在封装的时候是不会引出来了,也就是说在FT阶段这些模组很难甚至无法测量。在这样的情况下,测试就必须在CP阶段进行。这也是必须进行CP测试的一个重要原因。

还有一种特殊情况,芯片的封装是SIP之类的特殊形式。一方面这种封装形式在FT阶段可测性较低,而且多芯片合封的情况下,整体良率受每颗die的良率影响较大,所以一般需要在封装前确保每颗die都是好品 (KGD: Known Good Die)。这种情况下,往往无论多困难,都需要在CP阶段把所有测试项目都测一遍了。

所以,基于以上的认识,我们就比较容易在具体项目中判断CP测试项目的取舍了。

简单而言:

1) 因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的。而CP阶段则是可选。

2) CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目。凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测。些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作。在FT阶段再确认具体的SNR/THD等指标。

3) 由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选。精细严格的测试放到FT阶段。

4) 如果封装成本不大,且芯片本身良率已经比较高。可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺。

5) 新的产品导入量产,应该先完成FT测试程序的开发核导入。在产品量产初期,FT远远比CP重要。等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试。