第四章 – 積體電路規格表

經過第三章開路與短路測試的介紹後,讀者應該有一點了解,甚麼是半導體測試。這個章節將要介紹,積體電路規格表,英文稱為Device Specifications。筆者將開路與短路測試提前介紹,其主要理由有二。(1)開路與短路測試,在積體電路規格表中,一般不會特別提到此測試項目。其量測方法及判斷方式,也不會出現在規格表當中。(2)讓讀者事先了解,半導體測試工程中的第一個測試項目,作為進入此一領域的軟身操。

大部份的書籍講義,會將此章節提前介紹。而此章節內容,會提到所有的測試項目。但是,要了解此章節所介紹的測試項目、測試原理與方法。對初學者而言,是比較困難的。如果您想在這個章節裡,了解到每一個測試項目,您需要花很多的時間。因為,還有很多的觀念,需要在後面的章節仔細解釋,讀者才有辦法融會貫通。否則,讀者會在這個章節,一下子接觸到太多的術語,一時之間將無法消化。建議讀者在這個章節裡,以名詞解釋的方向來閱讀即可。

通常,半導體測試的書籍或講義,會在這個章節,附上一顆實際的積體電路規格表(Device Specification),並逐一地解釋。這樣的作法,對於從事IC設計者,或資深有經驗的電子工程師而言,不會有太大的困擾。但對初入此領域,或較資淺的工程師而言,不是很恰當的安排。基於上述的理由,筆者針對此章節,將著重在,積體電路規格表中的測試項目,及其名詞解釋。至於測試原理與方法,由後面的章節逐一說明。在這個章節裡,希望讓讀者能了解到,為何須要積體電路規格表、及如何閱讀積體電路規格表。規格表中,有那些重要的測試項目與參數。如何判斷測試項目,是Pass或Fail。如何決定那些測試項目,是在何種狀況下,需要被執行。

積體電路規格表的種類

半導體測試,是無法採用通用的方式來設計的。其測試的項目,完全建立在規格表中,並且是唯一的。也就是說,每一個Device,就要一套相關的測試程式及測試輔助設備,如Probe Card,Socket等。或許有人認為,記憶體IC,可以採用相同的輔助設備或程式。筆者認為,這樣的考量也只是局部的問題,無法全面採用。因此建議,針對每一顆Device設計一套,才是比較正確的做法。如此,可以免除管理上的複雜度。並在量產測試時,比較不會有誤載的情況發生。

如果想要將半導體測試,發揮到淋漓盡致的話。首先,要瞭解您的測試對象。對Device多一分的了解,您就能多一分的發揮。因此,對任何一顆Device,在開發測試程式之前,須仔細閱讀IC規格表。一般IC設計公司,會具備Device 的設計規格書(Design Specification)、測試規格書(Test Specification)或Device資料規格表(Device Data Book Specification)。這些規格,是測試計劃的基礎。一般情況下,會在完成以上的資料及規格後,才會進行測試計劃。並且,將測試計劃書完成後,才會進行Device測試程式的開發。

所謂的設計規格書(Design Specification)。是Device設計之前,定義Device的功能與效能特性的文件。它包括電壓、電流的規格、Device的時序、及Device的功能描述。例如Device的供電電壓是2.5V,還是1.8V。是否有低耗電量的要求,如省電模式。操作頻率的快慢,是高頻還是低頻的操作模式。這些規格,取決於市場的需要。它可能是由IC開發公司的市場規劃部門人員提出,或由業務人員提出。也有可能是由IC應用者來定義。當然,產出後Device的特性及功能,須要符合設計規格書內,所規定的內容。這裡有一個觀念,需要與讀者探討的是,在製造的過程當中,不是所有生產出的每一顆Device,皆能滿足規格書中所有的規格。例如DDR記憶體,有些顆粒,不能滿足設計規格書中規定的500MHz的操作頻率,但它能滿足400MHz操作頻率。這樣的舉例,讀者應該能瞭解,筆者希望表達的意思。

測試規格書(Test Specification)中,會詳細的描述測試的步驟與程序。一般而言,測試規格書,是提供給半導體測試人員使用。是經由相關單位及部門,共同完成的一份文件。它定義了,各種參數的實際電壓與電流值、測試Pattern,及Device的時序等。並在實際的測試情況下,依據此規格書的內容來測試,並判定每一顆Device,是否符合規格。並保證此Device,經過此測試程序,能完全符合規格。測試規格書中的測試參數,是會不斷的被修改的。其主要的原因,是因製程上的差異性,導致參數上的偏移。此時需要作適當的調整,來符合Device的特性。因此,當測試規格書,因某種因素而更改時,前面所提的設計規格書,也必須一併更改。

Device資料規格表(Device Data Book Specification),是依所發佈的文件整理出的。其內容包括Device的功能,及使用的特性。此文件,一般會稱呼它為 Data Sheet或直接稱呼為Spec。一般IC設計公司,會將這些文件,提供給所有的人。尤其會透過網路,發佈這些文件。英文的Data Book與Data Sheet或Spec之間的差異性,大致上可以這樣區分,Data Book會有比較詳細的規格定義。測試程式能依此文件來開發。而Data Sheet是提供給購買者,在應用上所需要的資訊。當然,其中也提供一些訊息,給測試程式開發人員,做為開發測試程式的參考。但是,並非每一家公司,都如此區分

規格表用語與量測概念

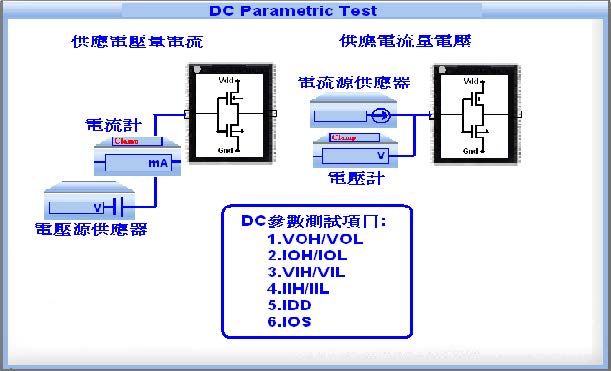

將介紹一些測試工程中的幾項專用術語。對資深的電子工程師,或許可以跳過此章節。而測試工程師,在閱讀規格表時,重要的是要瞭解到,三個主要的測試項目。這三個主要的測試項目是。(一)直流參數。(二)功能參數。(三)交流參數。其實,對測試工程師而言,就是要對這三大項的參數,進行測試的活動。所謂的直流參數測試,就是對Device做直流特性測試。例如,各種狀況下的電流量測、漏電流的量測,或是輸出電壓的量測等等。

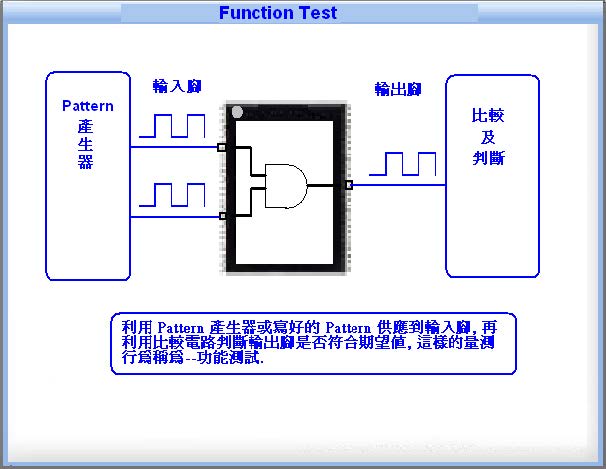

功能參數測試,一般會稱呼它為動態功能測試。也就是實際模擬Device在操作模式下,是否達到應有的電壓準位輸出。功能參數測試時,提供每一支輸入腳的各種可能狀況,然後去量測輸出腳的輸出,是否滿足規格表中的要求。

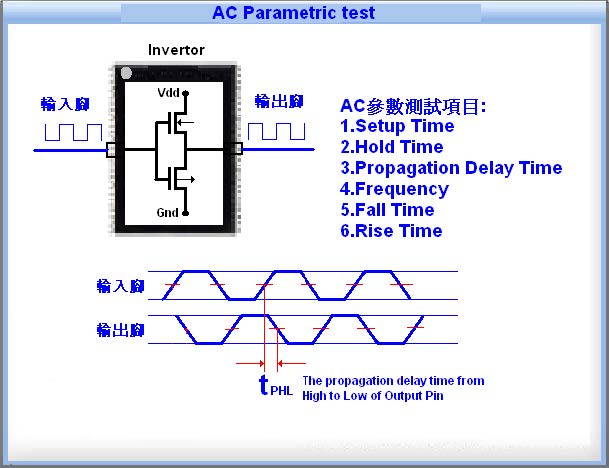

交流參數測試(也稱交流特性測試),也就是時間的量測。簡單地說,對輸出腳而言,其電壓的轉變過程當中,在什麼樣的時間之後,要達到電位的轉變。這個時間長度,就是所謂的交流參數的測試。一般交流參數測試。包括Setup Time、Hold Time、Fall Time及Speed這四大項。所謂的Setup Time、Hold Time以下會逐一說明。

圖1:直流參數量測概念

圖2:功能參數量測概念

圖三: 交流參數量測概念。

以下是規格表中的一些專用術語及符號:

VCC:

TTL電路的供應電壓。

ICC:

TTL電路的耗電流量。

VDD:

CMOS電路的供應電壓。

IDD:

CMOS電路的耗電流量。

Gross IDD;

Device在一種比較寬鬆的操作情況下,所量得的耗電量。

Dynamic IDD:

Device在一種比較頻繁的操作模式下,所量得的耗電量。

Static IDD:

Device在一種固定的操作條件下,所量得的耗電量。

VIH:

輸入腳在邏輯1時的最小電壓值(Input Voltage in High)。

VIL:

輸入腳在邏輯0時的最大電壓值(Input Voltage in Low)。

IIH:

輸入腳在邏輯1時的漏電流量(Input Leakage in High)。

IIL:

輸入腳在邏輯0時的漏電流量(Input Leakage in Low)。

VOH:

輸出腳在邏輯1時的最小電壓值(Output Voltage in High)。

VOL:

輸出腳在邏輯0時的最大電壓值(Output Voltage in Low)。

IOH:

輸出腳在邏輯1時的電流值(Output Current in High)。

IOL:

輸出腳在邏輯0時的電流值(Output Current in Low)。

IOZ:

輸出腳在Tri-State 狀況下的漏電流量(Output Current in Z state)。也稱為Output High Impedance Leakage Current。Tri-State/Z-State 也有人稱為High Impedance。

IOZH:

雙向腳在邏輯1時,被驅動為Tri-State 狀況下或OFF的情況下的最大漏電流量(Output High Impedance Leakage Current High)。

IOZL:

雙向腳在邏輯0時,被驅動為Tri-State 狀況下或OFF的情況下的最大漏電流量(Output High Impedance Leakage Current Low)。

Static:

靜態。Device在某一種固定的模式運作時的狀態,稱之為Static。通常量測直流參數時的狀態,會採用Static模式。

Dynamic:

動態。Device在各種不同條件運作的狀態,稱之為Dynamic。尤其是測試向量在執行時的狀態。

Precondition:

前置條件,這是一個對Device操作的一般概念。當我們希望在某種狀態下量測電壓或電流值時,Device需要被驅動到想要的條件下,這樣的動作,稱之為Precondition。有時候,某些測試項目的測試條件,需要先做Precondition。而Precondition不會在規格書中說明。這是需要讀者學習過程中,特別注意的地方。

測試條件,一般人較能體會其意義。尤其是純數位積體電路測試時,給予的電壓或電流值。舉例而言,如果希望在Vdd=VddMin時,測試VOL參數,此時Vdd=VddMin就是測試條件。如果規格書中VOL Max=0.4V時,我們所量測出來的電壓值,最大不能大於0.4V。否則會判斷為Fail。而VOL Max=0.4V就是條件限制(Test Limits)。

■ 直流參數量測時,應特別注意以下的幾項參數,是否於規格表中說明:

(1)輸入腳電壓及電流(VIL,VIH,IIL,IIH)。

(2)輸出腳電壓及電流(VOL,VOH,IOL,IOH,IOZL,IOZH)。

(3)電源供應電壓及電流(Vcc,Vdd,VddMax,VddNom,VddMin,Icc,Idd)。

(4)每一種參數的Pass/Fail條件。

■ 功能及交流參數量測時,應特別注意以下的幾項參數。是否於規格表中說明:

(1)VIL,VIH的輸入條件。

(2)VOL,VOH,IOL,IOH的輸出條件。

(3)電源供應電壓(Vdd,VddMax,VddNom)。

(4)時序(Frequence,Plus Widths,Setup Time,Hold Time,Delay Time)。

(5)每一種參數的Pass/Fail條件。

Device的邏輯功能:

一般簡單的邏輯IC,會用真值表來加以說明。而複雜的Device,可能須要相當多的微指令,才有辦法說明其功能。

積體電路規格表的內容

一般積體電路規格表,會包括以下幾項訊息。

(1)Device的一般描述(Description)。

(2)特性及功能說明(Feature)。

(3)Device的接腳圖例(Pin Configurations)。

(4)功能方塊簡圖(Block Diagram)。

(5)電性規格(Electrical Specifications)。

(6)接腳說明(Pin function)。

(7)指令說明(Command Operation)。

(8)操作及應用說明(Device Operation)。

(9)時序定義(Timing Waveform)。

(10)其他相關訊息。

這個章節,會針對這些重要的部份,以簡要的方式說明。主要是要給讀者一個概念而已。

Device的一般描述(Description)

| HITACHI HD74LS174/HD74LS175 D Type Flip-Flop Description These positive-edge-triggered flip-flops utilize TTL circuitry to implement D-type flip-flop logic. All have a direct clear input, and the HD74LS175 features complementary outputs from each flip-flops. Information at the D inputs meeting the setup time requirement is transferred the Q outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D input signal has no effect at the outputs. |

以上這段是HITACHI D Type Flip-Flop的一般描述(Description)。因這顆IC,是一顆很簡單而不複雜的邏輯電路。以簡略的敘述,就能充分說明其用途。它簡略說明了這顆IC有兩種規格,是屬於TTL電路的一種。採正向觸發的D Type正反器。各位如果對邏輯電路,有一些印象的話,正反器是可以拿來,當作記憶體之用。並且告訴我們,這兩種規格皆有一支Clear(清除)輸入腳。HD74LS175具有補數輸出腳/Q。當Clock Pulse(時脈訊號)的正向邊緣發生的那一個時間點,輸入腳D所代表的訊息,會被傳送到Q的輸出腳上。也就是說,D如果是1,則Q就會是1。並且不管Clock Pulse(時脈訊號),是在高電壓或低電壓下,D的輸入訊號,不會影響到Q的輸出訊號。

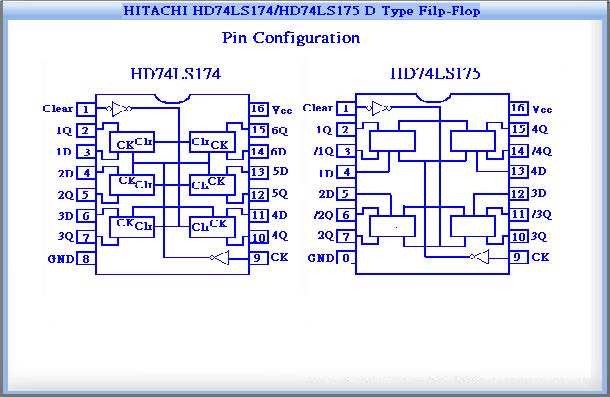

- Device的接腳圖例(Pin Configurations)

圖A

圖A是HITACHI HD74LS174/HD74LS175 D Type Flip-Flop晶片的接腳圖。說明每一支接腳的名稱及功能。至於內部的線路圖,一般是不會畫出來。除非只是簡單的一顆邏輯IC。

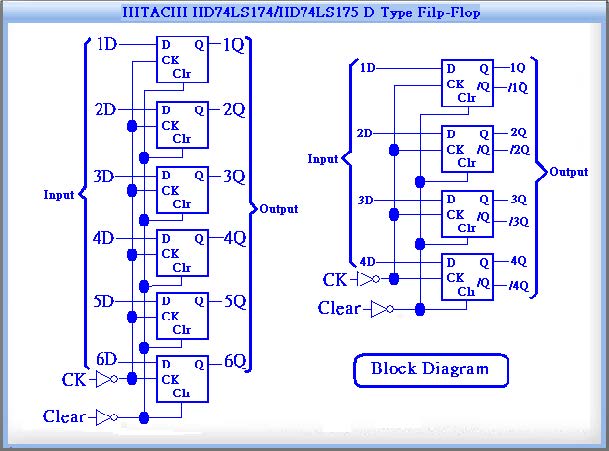

4. 功能方塊簡圖(Block Diagram)

圖B

圖B是HITACHI HD74LS174/HD74LS175 D Type Flip-Flop晶片的功能方塊圖。以邏輯結構的方式說明其功能。

- 電性規格(Electrical Specifications)

會包括最大額定範圍(Absolute Maximum Rating)。例如最大溫度範圍、最大電壓範圍、最大電流範圍等等。還有操範圍(Operation Rating)。例如Vdd的操作電壓,及操作溫度。一般,商用規格與軍用規格,會在此有比較大的差異。軍用規格,在電壓及溫度的變化上,會比較大。各項直流參數,一般會用表列的方式來敘述。與輸入腳有關的參數有VIH、VIL、IIH、IIL。與輸出腳有關的參數有VOH、VOL、IOH、IOL。與Power Pin有關的直流參數有Icc電流,或Idd電流。輸入及輸出腳的電容值(Capacitance),對系統設計工程師而言,是一項很重要的直流參數。但對數位半導體測試而言,一般會忽略它。

以下是以HITACHI HD74LS174/HD74LS175 D Type Flip-Flop晶片,作為範例說明規格書的內容。

■ VOH參數:輸出腳在邏輯1時的最小電壓值(Output Voltage in High)。

| Symbol | Description | Test Condition | Min | Max | Unit |

| Vol | Output Voltage | Vcc=4.75,VIH=2V,VIL=0.2V,IOH=-400μA | 2.4 | – | V |

這樣的VOH參數規格表,說明了VOH參數的測試條件,及測試後的判斷標準。

(1) Vcc電源供應電壓為4.75V。在實際的規格表中,Vcc = VccNom = 5.0V,VccMin = 4.75V,VccMax = 5.25V。測試VOH參數時,是給予Vcc = VccMin = 4.75V。這個用意,希望在最壞的供應電壓狀況下,期望其輸出腳電壓,是否仍能達到應有的標準。

(2) 輸入腳的電壓準位為VIH=2.0V,VIL=0.2V。VOH參數是對輸出腳作量測。同時,我們要提供輸入腳的邏輯電壓值,才會讓輸出腳處於邏輯1的狀況。這個動作也就是Precondition的意思。

(3) 以上準備就緒後,利用電流源供應器供應一個-400μA的電流,也就是IOH=-400μA。然後用電壓計,量測輸出腳的電壓。

(4) 所量得的VOH電壓,最小值應為2.4V。如果大於或等於時,則Pass,否則Fail。這裡告訴我們,沒有最大值的要求。但我們可以理解,其電壓值應不會大於Vcc的4.75V。

■ VOL參數:輸出腳在邏輯0時的最大電壓值(Output Voltage in Low)。

| Symbol | Description | Test Condition | Min | Max | Unit |

| Vol | Output Voltage | Vcc=4.75,VIH=2V,VIL=0.2V,IOL=4mA | – | 0.4 | V |

(1) Vcc電源供應電壓為4.75V。在實際的規格表中,Vcc = VccNom = 5.0V,VccMin = 4.75V,VccMax = 5.25V。 測試VOL參數時,是給予Vcc = VccMin = 4.75V。這個用意是,希望在最壞的供應電壓狀況下,期望輸出腳電壓,是否仍能達到應有的標準。

(2) 輸入腳的電壓準位為VIH=2.0V,VIL=0.2V。VOL參數是對輸出腳作量測,同時,我們要提供輸入腳的邏輯電壓值,才會讓輸出腳處於邏輯0的狀況。

(3) 以上準備就緒後,利用電流源供應器供應一個4mA的電流,也就是IOL=4mA。之後,用電壓計量測輸出腳的電壓。

(4) 所量得的VOL電壓最大值應為0.4V。如果小於或等於時,則Pass,否則Fail。這裡告訴我們,沒有最小值的要求。

■ VIH/VIL參數:輸入腳在邏輯1/0時的最小/最大電壓值(Input Voltage in High/Low)。

| Symbol | Description | Test Condition | Min | Max | Unit |

| VIH | Input Voltage | 2.0 | – | V | |

| VIL | Input Voltage | – | 0.2 | V |

這樣的VIH/VIL參數規格表。說明了VIH/VIL參數的最大最小值。當要驅動輸入腳,並且讓輸入腳為邏輯1時的最小電壓值為2.0V。當要驅動輸入腳並且讓輸入腳為邏輯0時的最小電壓值為0.2V。一般來說VIH/VIL是很少需要測試的。所以有些規格表並未說明VIH/VIL的測試條件。

■ IIH/IIL:輸入腳在邏輯1/0時的漏電流量(Input Leakage in High/Low)。

| Symbol | Description | Test Condition | Min | Max | Unit |

| IIH | Input Current | Vcc=5.25V,VI=2.7V | 20 | μA | |

| IIL | Input Current | Vcc=5.25V,VI=0.2V | – | -0.4 | mA |

(1) IIH 的量測條件是,Vcc=5.25V,而待測腳要供應一個電壓,讓待測腳處於邏輯1的情況,此電壓值就是Vi=2.7V。所量得的漏電流量不可大於20μA。

(2) IIL 的量測條件是,Vcc=5.25V,而待測腳要供應一個電壓,讓待測腳處於邏輯0的情況。此電壓值就是Vi=0.2V。所量得的漏電流量,不可大於-0.4mA。

■ IOZ:輸出腳在High Impedance狀況下的漏電流量(Output High Impedance Leakage Current)。這個參數不是HD74LS174/HD74LS175的規格參數。筆者只是隨便舉個例子。

| Symbol | Description | Test Condition | Min | Max | Unit |

| IOZ | Output Current(High Z)Output Current(High Z) | Vss≦Vout≦Vdd, Outputs Disabled | -10 | 10 | μA |

(1) 要量輸出腳在High Impedance狀況下的漏電流量。首先要將輸出腳關掉(Off)或稱Drive to High Impedance。這個動作,也就是Precondition。一般需要執行一小段的測試向量,才能達到這個狀態。測試條件中的Outputs Disabled就是這個意思。

(2) 而Vss≦Vout≦Vdd的意思是,輸出腳在邏輯1時,供應的電壓值(Vout=Vdd),而一般此時的Vdd=Vddmax。

(3) 輸出腳在邏輯0時,供應的電壓值(Vout=Vss=0V)

(4) 所量到的漏電流量,不可大於10μA或小於-10μA。

■ ICC: TTL電路的耗電流量。

| Symbol | Description | Test Condition | Min | Typ | Max | Unit |

| ICC | Power Supply Current | Vcc=5.25V | – | 11 | 18 | mA |

(1) 測試條件為供應電壓Vcc=5.25V。為何要用Vcc=VccMax=5.25V?其原因在於,給予較高的電壓下,量測耗電量。此時的耗電量不可大於18mA。如果供應電壓用Vcc=5.0V或Vcc=4.75V,有可能最大耗電量不會大於18mA。但用Vcc=5.25V時,有可能大於18mA。

(2) 耗電量不需考慮最小值。在要求環保的前題下,省電是一種最直接的作為。如果能設計出不耗電的IC。人類的文明,可能將是現代人,無法想像的境界。

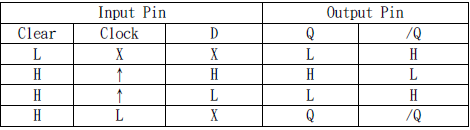

7. 指令說明(Command Operation)

指令說明(Command Operation)或操作及應用說明(Device Operation)。對於複雜的IC而言,需要不算短的篇幅來解釋。以HITACHI HD74LS174/HD74LS175 D Type Flip-Flop 為例。可以用以下的真值表,即可清楚的說明。

(1) Clear Pin 為Low(0)時,忽略Clock Pin 及D Pin的邏輯狀況。Q Pin會是Low(0),而/Q Pin會是High(1)。

(2) ClearPin 為High(1)時,且Clock剛好由Low(0)轉High(1)的那一剎那,如果D Pin為High(1)則Q Pin就為High(1),同時/Q就為Low(0)。如果D Pin為Low(0)則Q Pin就為Low(0),同時/Q就為High(1)。

(3) ClearPin 為High(1)時,且Clock為Low(0)時,並忽略D Pin。此時Q Pin及/Q Pin為維持原有的狀況。就是這樣的行為,可以當成記憶體來使用。

9. 時序定義(Timing Waveform)

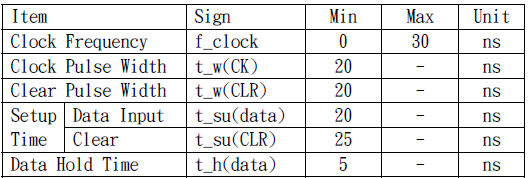

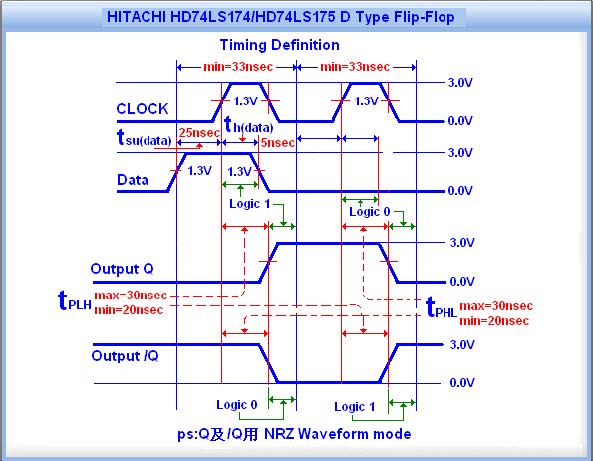

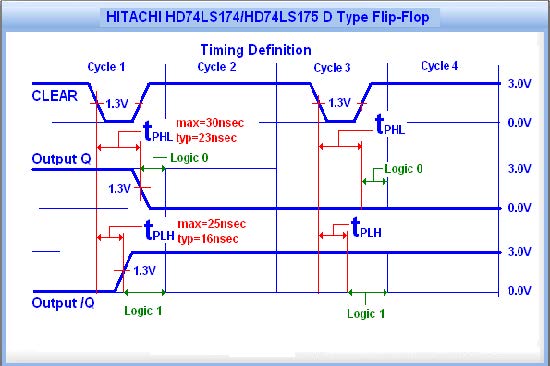

時序定義(Timing Waveform)。一般會提供Pin 與Pin之間的時序關係(Timing Definition)、建議的操作條件(Recommended Operating Condition)、切換特性(Switching Character)。以下逐一說明。

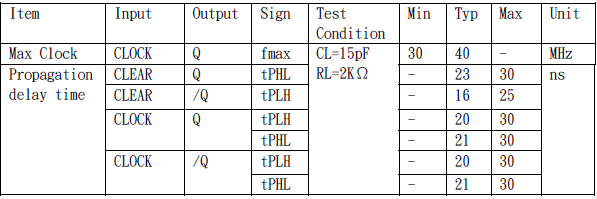

切換特性(Switching Character)

建議的操作條件(Recommended Operating Condition)

有時候,規格書中提供的時序圖,並不很容易理解。讀者有可能會解讀錯誤。規格撰寫者為了減少篇幅,或希望以較少的圖表,來表達以上的訊息,所導致的結果。筆者為了解釋以上的參數,並不想用原版規格書所提供的圖表。以下是筆者針對以上參數,逐一繪圖而成。並希望如此能讓初學者,逐一瞭解各參數的意義。

首先,先介紹幾個專業術語。所謂的延遲時間(Propagation Delay Time),就是利用輸入腳輸入一個指令(或稱控制訊號,或稱Pattern)後,希望在輸出腳得到想要的訊號(或稱邏輯值,或稱高低電壓皆可)。 如果設計的IC效能很好的話。在輸入的同時,也能在輸出腳得到訊息。這樣也就沒有所謂的延遲時間的問題。但是目前積體電路中,不管是TTL電路或CMOS電路,還未能達到此境界。

因此延遲時間,勢必存在於積體電路中。讀者可以想像販賣機的情況,投幣後要等一下子,東西才會掉下來。所以延遲時間,是輸入腳與輸出腳之間,時間差異的一種關係。所以呢!切換特性表中(Switching Character),一定會有輸入腳與輸出腳的欄位。兩支輸入腳與輸出腳會有不同的延遲時間參數。例如CLOCK與Q之間會有tPHL與tPLH兩種延遲時間參數。

Setup Time筆者翻譯成準備時間。筆者如此翻譯的主要原因,是要加強記憶。Setup Time與Hold Time,是用來描述輸入腳與輸入腳之間,訊號波形的相關性。以範例來講,Data 輸入腳與CLOCK腳之間,就存在Setup Time與Hold Time的關係。在真值表中有描述,當CLOCK訊號,由低電位轉變為高電位的那一剎那(正向邊緣觸發),輸出腳Q的邏輯值,要與Data腳的邏輯值相同。為了達到這樣的目的,我們需要在Data腳,事前給予一個邏輯值。

而何時就要準備好這個邏輯值呢?這個準備時間就是Setup Time。準備好後,需要一段時間的維持這個邏輯值。就是這個Hold Time(維持時間)。維持時間是當CLOCK訊號來臨後,能有一段時間讓輸出腳Q,可以參考到這個Data腳的邏輯值。以範例來講,CLOCK腳的正向邊緣觸發訊號,來臨之前的這段準備時間,稱為Setup Time。CLOCK腳的正向邊緣觸發訊號,來臨之後的這段維持時間,稱之為Hold Time。當然這只是一個舉例,重點要知道的是,兩支輸入腳之間的關係。在真值表中,所具備的功能及角色的扮演。因此,接腳說明(Pin Function),是很重要的一個訊息來源。

公式:週期(T)=1/頻率(f)。這個很重要不可忘記!

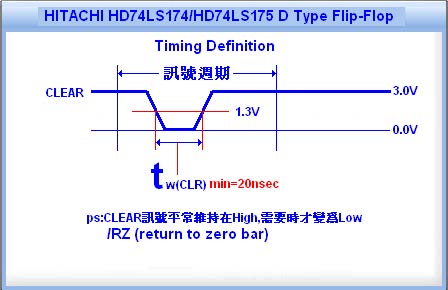

圖A: Clear Pin其訊號寬度 min=20nsec。

圖B

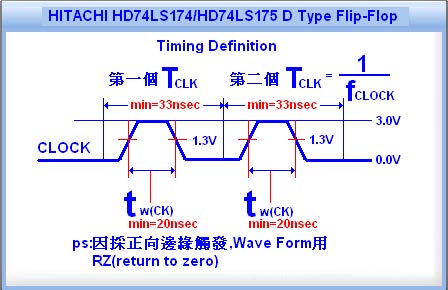

Clock Pin其訊號寬度(Duty Cycle) min=20nsec及操作週期。這裡有提到Waveform的觀念讀者不必急於瞭解,甚麼是Waveform。後面的章節會有詳盡的說明。

圖C

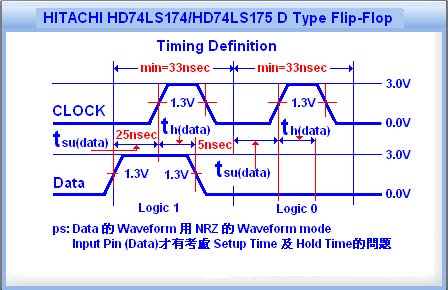

Clock Pin與Data Pin之間的關係。兩者為輸入腳,故有Setup Time與Hold

Time的問題。 第一個Cycle, Data Pin 的邏輯值為1。第二個Cycle, Data Pin 的邏輯值為0。在Hold Time的這段時間內,Data的邏輯值對此Device而言,才有意義。

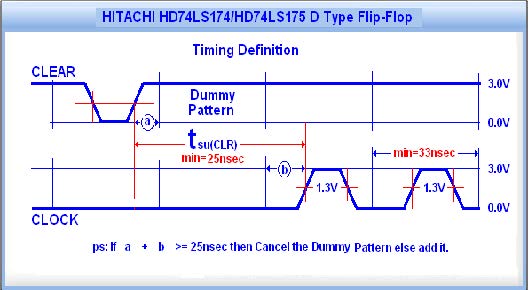

圖D

Clear Pin與Clock Pin兩者為輸入腳。當Clear訊號回到High,並經過一段時間後,Clock的正向邊緣觸發訊號,才開始有意義。特別注意這個Dummy Pattern。如果您在定義Clear及Clock訊號波形,無法滿足 a+b >= 25nsec的基本要求時,加上一個Dummy Pattern,應該就可滿足要求。

圖E

圖E主要是要說明 Clock Pin 與 Output Q及Output /Q的延遲時間。本來,不想將Data Pin加入,怕圖會太複雜。但考慮後,認為三者之間是有相互關係的。Output Q及Output /Q 在這兩個Cycle內,只有綠色區間,代表其邏輯值。因此,在執行功能測試時,記得將Strobe Time 定在這個區間內。

圖F

圖F。Clear Pin與Output Pin之間的延遲時間。Clear Pin的意義就是將Output Pin清為邏輯0的動作。