第二章-半導體測試基本概念

半導體產品,一般稱為積體電路。英文稱為 Semiconductor Device。Device在中文意義為『設備』或『裝置』。然而對『設備』或『裝置』一詞,通常情況下,是對整體的機械設備,作翻譯與解釋。而Device在半導體測試領域裡,指的是半導積體電路而言,通常都用IC來稱呼。如果將 Device ,直接翻譯為設備,較不恰當。因此,本書往後,直接用英文Device稱乎,而不翻譯它。

這個章節,會從測試基本用語作介紹。讓工程師們,對半導體測試,有一番基礎的認識。並且簡介測試機應俱備的基本功能。

半導體測試用語

DUT

DUT是Device Under Test的縮寫,中文直稱為待測物。有時,也稱待測單元UUT(Unit Under Test)。

IC接腳 ( Pin)

IC設計者,會利用接腳傳遞訊號,這些接腳英文稱為Pin。積體電路裡,有各種不同用途及功能的接腳。例如訊號腳,它包括輸入腳(Input Pin)、輸出腳(Output Pin)、三態腳(Tri-State Pin)、雙向腳(Bi-direction Pin)等。電力腳,包括電源供應腳(Power Pin)及接地腳(Ground Pin),此兩種接腳,不屬於訊號腳。訊號腳與電力腳,主要的不同在結構上的差異。此差異,一般會在半導體設計書籍中,詳加介紹。

如下分類逐一說明:

輸入腳(Input Pins)

輸入腳,可以想像它是介於外部訊號和內部邏輯電路的一種緩衝裝置。”輸入(Input)”一詞,意味著將某一電壓值,供應到輸入接腳上,並且傳遞一個邏輯訊號0或1,到Device內的邏輯電路。

輸出腳(Output Pins)

如同輸入腳一樣,可以把它當成外部環境與Device內部邏輯電路的緩衝器。輸出腳,必須提供正確的電壓,由此電壓來判定是邏輯1或邏輯0。同時,也必須提供 IOL/IOH 的電流量。IOL(Output Current in Low)是輸出腳在代表邏輯值0時,所容許的最大電流值。IOH(Output Current in High)是輸出腳在代表邏輯值1時,所容許的最小電流值。後面的章節,會有專章詳細說明,這些測試用語。如VIH、VIL、VOH、VOL等等。

三態輸出腳(Three-State Output Pins)

此種輸出腳,除了具備一般輸出腳的功能之外,還具備開關的能力。所謂開關的能力,是可以讓三態腳,處於高阻抗的狀態(High Impedance State)。而高阻抗狀態,就是其輸出電壓小於VOH,且大於VOL的值。英文還有另一種稱乎,叫做Tri-State。

雙向腳(Bi-Directional Pin)

雙向腳,可以具備一般輸出腳及輸入腳的功能之外。如三態輸出腳一樣,具備開關的能力。

電力腳(Power Pin)

電力腳,包括電源供應腳(Power Pin)及接地腳(Ground Pin)。CMOS電路的電源供應腳,稱為VDD。TTL電路的電源供應腳,稱為VCC。TTL電路,稱 VSS為接地腳。然而,訊號腳與電力腳的不同,主要在於結構上的差異。

VCC腳

TTL電路的電壓源供應腳。

VDD腳

CMOS電路的電源供應腳。

VSS腳

此種電力腳,會使電路形成一種迴路的接腳。VSS在TTL電路及CMOS電路皆有使用。

接地腳(Ground)

接地腳的主要目的,是連接訊號腳與測試系統的參考點(或VSS腳)形成迴路,或者讓其它電子迴路接點,與測試系統的參考點(或VSS腳)形成迴路。如果一個Device,只有一支電源供應腳的時候,VSS腳通常被稱乎為 ” Ground “。

半導體測試

半導體測試的主要目的,是利用測試機執行被要求的測試工作。並保證其所量測的參數值,是符合設計時的規格。而這些規格參數值,一般會詳細記錄於的規格表內。待測物的規格表,英文稱為Device Specifications。

一般測試程式會依測試項目,區分成幾種不同的量測參數。例如直流測試(DC Test)、功能測試(Function Test)、交流測試(AC Test)。直流測試,是驗證Device的電壓與電流值。功能測試,是驗證其邏輯功能,是否正確的運作。交流測試,是驗證是否在正確的時間點上,運作應有的功能。

測試程式,是用來控制測試系統的硬體。並且對每一次的測試結果,作出正確(Pass)或失效(Fail)的判斷。如果測試結果,符合其設計的參數值,則Pass。相反地,不符合設計時,則為Fail。測試程式,也可以依測試結果及待測物的特性,加以分類。這個行為,英文稱為 「Binning」。有時也稱為 「Sorting」。例如:一顆微處理器,在200MHz的頻率之下運作正常,可以被分類為A級「BIN 1」。另一顆處理器,可能無法在200MHz的頻率下運作,但可以在100MHz的頻率下運作正常,它並不會因此被丟棄。可以將它分類為 B 級「BIN 2」。並且將它賣給不同需求的客戶。

測試程式,除了能控制本身的硬體之外,也必須能夠控制其它的硬體設備。例如:分類機(Handler)、針測機(Prober)等。此設備具有機械手臂或類似機構,可以拿起及放下待測物(此待測物一般是已封裝好的積體電路)。其拿起的位置及擺放的位置,可以藉由程式來控制。針測機(Prober),也可以稱呼它為晶圓針測機,Probe英文字意為探針,探測的意思。但Wafer Prober設備,並不具備探測的能力。它只是將晶圓片,載入機台內,並將晶圓片與測試頭的測試探針,做正確的接觸,以便執行測試的工作。測試程式,必須能夠收集測試結果。並將結果,以統計的方式或其它方法,形成測試報告。讓產品工程人員能夠依此報告,改善製程良率。

然而,對半導體測試而言。什麼是正確的測試方法呢? 時常有人提到,這個問題。 很不幸地,正確的測試方法,並沒有唯一的定義。而且,也沒有最佳的標準答案。對某一種狀況的滿足,並不足以滿足其他的狀況。有許多因素,會影響測試程式的開發。以下,我們將舉出幾種因素及目的,分別加以探討。開發測試程式之前,首先要了解測試的目的? 測試的時機? 測試的需求等等。這樣才會開發出最適合的測試程式。以下逐一說明。

Wafer Test

所謂的Wafer Test。是說Device還排列在晶圓片上,尚未切割前,所進行的測試過程。Wafer Test是半導體製作過程中,將Device區分為好品或壞品的第一次測試。因此,被稱為Wafer Sort或Die Sort。有時,也簡稱為 CP Test。英文的Die,代表單一顆粒的用詞,與實際原字意不相同。Wafer英文原字意為薄餅,用來代表晶圓片。

Package Test

Wafer被切割成一顆顆的裸晶Dice(複數),並且將每一顆裸晶Die(單)封裝成Package形式。封裝好的Device成品。經過 Package Test測試過程,以確保封裝的過程是否正確。並且保證Device,仍然符合設計上的要求。Package Test,有時候也稱為Final Test(簡稱FT Test)。

Quality Assurance Test

品質確認測試。以單顆Device為測試對象,確保 Package Test可以正確執行。

Device Characterization

Device 特性驗證。是針對單一Device而言,測試其參數的極限值。此種測試目的,稱為特性驗證測試。

Pre/Post Burn-In

Burn-In前與Burn-In後的測試,主要用來確認Burn-In程序不會引起某些參數的偏移。Burn-In這個程序,可以除掉初期(前期) 失敗的顆粒。所謂初期失敗的顆粒,是這些顆粒製造時,有一些暇庛,導致使用時,很快就壞掉而無法使用。

Military Testing

軍規測試,屬於比較嚴格的效能測試。一般會橫跨高溫與低溫的測試。一般概念中,軍規測試的條件,會比較嚴謹。

Incoming Inspection

進貨檢驗。一般IC使用者,會在採購進貨時,所作的檢驗測試。確保使用前是良品。

Assembly Verification

組裝驗證。所謂的組裝驗證,就是將IC,利用SMT設備或手工方式,焊接到PCB板上之後,所進行的功能驗證程序。

Failure Analysis

失效分析(Failure Analysis)的主要目的,是探討失效造成的原因。以便提出改善方法,增加其信賴度。失效分析的過程當中,通常會藉助測試系統與程式,在某些特殊條件與狀況下,來執行測試的程序。

測試機台的基本功能

一般測試機台,會依據測試的對象,作專屬的功能設計。例如記憶體測試機,在開發記憶體測試程式時,會提供比較多關於記憶體測試所需要的功能及測試便利性的考量。因此,各種不同的測試機台,會有不同功能的設計。

高效能測試機具備的幾點特性

(1) Highly Accurate Timing

具備高精密度的時序電路

(2) Large Vector Memory

具備較大的測試向量記憶體容量,可減少測試向量,重新載入的次數

(3) Multiple PMUs

多重PMU量測單元。具備平行處理能力,以減少直流測試項目的測試時間。

(4) Programmable Current Loads

可程式化的電流負載。可簡化測試系統的硬體設計。並且增加彈性。也稱為 Dynamic Loads 或 Active Loads。

(5) Timing and Level per Pin

每一根測試通道(Channel),皆具備時序與準位的設定,還有驅動能力的選擇。使得程式的開發更加容易,並且可減少測試時間。

低成本測試機的特性

(1) Low Speed/Low Accuracy

低速及低精準度的特性。有時無法滿足IC測試規格上的要求。

(2) Small Vector Memory

具備較少的測試向量的記憶體容量,測試向量重新載入的次數會比較多。

(3) Single PMU

單一PMU量測單元。在直流測試時,只能依次序量測。因此,在單項量測時,所花的時間會比較久。

(4) Shared Resources(Timing/Levels)

時序及準位,採用共享資源的方式。這樣的設計,在測試程式開發上,是比較複雜且不容易開發的。測試時,所需要的測試時間,也會比較長。成本這個因素,通常是用來決定,是否測試的最後關鍵。

測試程式,對程式開發工程師而言,基本上,是建立在特殊的需求上。過去的經驗中,售價會影響測試項目與內容。測試程式開發之前,測試工程師,必須考慮到每一個測試項目的各種狀況,以便找出一個最佳的解決方案。通常在測試程式設計上,沒有對與錯的問題,只有適合與不適合的問題。

測試系統

測試系統,是由電子電路及機械結構,所組合而成的一種裝置。被用來模擬各種環境,並檢測IC是否仍能正常運作的一套系統。一般稱為ATE(Automated Test Equipment)。所有的硬體,皆由電腦所控制。它可以執行一連串的指令,這些指令的集合,稱為測試程式。測試系統,必須要能夠提供正確的電壓、電流、時脈訊號等等條件。並且,監測每一次測試項目的回應值。測試系統,會比較每一次測試的結果,與事先定義的期望值是否相符。並加以判斷,IC是正常(Pass)或失效(Fail)。通常情況下,測試系統是由電源供應器、量測器、訊號產生器、測試向量產生器等硬體,所組合而成。

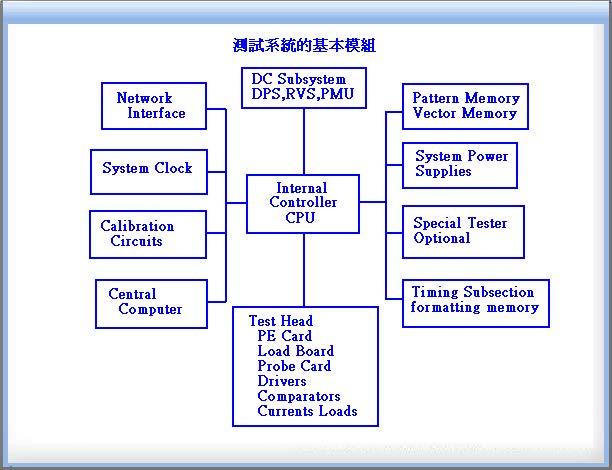

圖: 說明一般測試系統俱備的基本模組。目前,有很多新的測試系統,提供更多的功能。圖中的CPU是扮演系統控制器的角色。它是一部具備微處理器的電腦,可以控制測試系統。並且提供資料進出測試系統的能力。目前,大部份新的測試系統,具備網路介面能力,以便能與外界進行資料的交換。

DC子系統,包括DPS (Device Power Supplies)、RVS ( Reference Voltage Supplies )和PMU ( Precision Measurement Unit )。DPS會供應電壓及電流,給待測物的電源接腳Power Pin(Vdd/Vcc)。RVS具備提供邏輯準位參考電壓,以便判斷是否為邏輯0或邏輯1。並具備比較電路,以便與這些VIL、VIH、VOL、VOH的電壓設定值作比較。低成本或舊式測試系統,只具備極少數量的RVS供應器。所以只能供應有限數量的輸出入邏輯準位。

當測試系統的測試通道(Test Channel),以分享或共用的方式提供資源時(例如RVS),這種結構,稱之為資源分享式結構(Shared Resource)。有些測試系統,標榜具備Per Pin結構。Per Pin結構的意義是,測試系統,可以對待測物的每一根腳位,提供獨立的輸出準位設定、輸入準位設定及時序設定。此一硬體設計,

稱之為『Per Pin結構』。Test Channel也可以稱為Test Pin。Test Pin是設計在PE Card上的邏輯電路,它可以供應電壓或電流,及提供時序訊號給待測物。PMU(Precision Measurement Unit)高精密量測單元,可以提供精準的DC參數的量測。有些測試系統,具備 Per Pin結構的PMU單元。

大部份的測試系統,會具備一組高速記憶體,稱為Pattern Memory或Vector Memory。此記憶體主要的目的,是用來存放測試向量或測試Pattern的地方。測試Pattern,如同大家所熟悉的真值表。用以代表輸入腳與輸出腳的各種不同邏輯狀態。測試機,將存放在高速記憶體的Pattern,輸入(或稱驅動)到待測物的輸入腳位上,然後在輸出腳位上,量測電壓值。以便與高速記憶體上,存放的Pattern值作比較。一般,功能測試(Function Test)時,測試向量(Pattern)所記載的邏輯值,會被輸入到待測物上。並且量測輸出腳的邏輯值,以便與事先記載於Pattern的內容作比較。如果不相符時,測試機,會判斷為功能失效(Functional Fail)。一般測試向量,分為兩種型態,Parallel Vectors(平行向量)及Scan Vectors(掃瞄向量)。許多測試系統,具備此兩種型態的測試向量。

時序電路子系統,在設計上會有記憶體的設計,以便存放格式化的資訊(Format Data)、遮罩後的資訊(Mask Data)、時序設定資訊(Time Set Data)。尤其在功能測試時,會常用到。訊號格式Signal Formats(或稱訊號波形Wave Shapes),藉由時序電路,所產生時序邊界。也就是說,時序電路子系統,會從Pattern Memory接收到Drive Patterns。並且將接收到的Pattern與時序(Timing)及訊號,組合起來產生一組格式化的訊號。並將此訊號,傳送到待測物的每一根腳位上。

有些測試機製造商,為了商業上的考量,會設計一些特殊選項。例如邏輯演算測試向量產生器(ALPG)。這種產生器,可用來測試記憶體的邏輯功能。它是利用硬體的方法來設計,以便在執行測試時,能夠更加地快速。

測試系統必需提供系統時脈。系統時脈是讓訊號同步的一種方法。這個時脈訊號,遍及整個測試系統。這個系統時脈的頻率,通常會高於待測物的操作頻率。絕大多數的測試系統,具備校正電路。校正電路,是用來確認所有的驅動電路,是否提供正確的電壓電流值。同時也可以,用來校正系統時脈。

通訊處理能力。測試機,一般可藉由通訊介面,與其他設備,作資料及訊息的交換。例如Wafer Prober、Device Handler或其他測試設備。一般會用到的通訊介面有Serial Protocol或GPIB Protocol(IEEE-488)這兩類較多。

測試頭,一般包含有 Pin Electronics Card、連接到待測物的硬體設施,或者是Load board。Load board,是介於測試機和待測物之間一種硬體介面。經由它,可以將Test Socket及探針連接到待測物。一般Load board上,還會有一些零組件,例如繼電器(Relay)、電阻負載(Resistive Load)、解耦合電容(Power Supply Decoupling Capacitor)等。靠近測試頭的設備,還有測試控制盒 (Test box或稱Bin box)。很典型的測試控制盒,具備開始測試及重新測試的按鈕,並且會顯示Pass或Fail的訊息。

精密量測單元(Precision Measurement Unit),主要提供DC參數的量測。它可以提供電流,然後量測電壓(Current Force Voltage Measure)的量測方法,或者提供電壓後量測電流(Voltage Force Current Measure)的量測方法。某些測試系統,只提供一個精密量測單元(PMU)。當待測物的所有Pin須要DC量測時,才利用分享的方式來使用。有些測試系統,則不止提供一個精密量測單元(PMU),通常會以八個一組或十六個一組來設計。高檔的測試系統,會有Per Pin的PMU。也就是每一個Tester Channel,皆具備一個精密量測單元(PMU)。

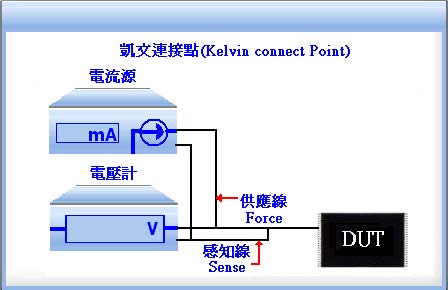

在供應電源的電路設計上(如供應電壓),有所謂的『凱文連接點』 (Kelvin Connect Point)。也就是說,利用兩條分開的線路,一條是感應線(Sense Line),一條是供應線(Force Line)。這樣的設計目的,是要保持電壓不會偏移。因為供應電壓線路的長短,會有電壓降的問題。當感應線感應到壓降時,電路上的設計,會自動提高電壓,以補償電壓的偏移。感應線(Sense Line)與供應線(Force Line)的連接點,我們稱為凱文連接點(Kelvin Connect Point)。

量測範圍的設定(Range Settings)。精密量測單元的供應範圍(Force Range)或量測範圍(Measure Rang),是必須要事先設定的。這意味著,精密量測單元,所供應的電壓或電流,是有範圍限制的。供應範圍(Force Range),是用來決定PMU最大供應能力。如果PMU設計能提供5伏特電壓,並且被設定供應電壓範圍為2伏特電壓。此時其最大供應電壓,只有2伏特。相同地,電流量測範圍被設定為1毫安培(1mA)時,此時所能量測的最大電流值為1毫安培 (1mA)。在此,必須要特別提醒的是,不管是供應範圍或量測範圍,都必須要在量測動作,未開始之前先設定好。如果在量測的過程中,改變設定範圍,會引起瞬間凸起雜訊(Noise Spikes)。此雜訊,可能會破壞待測物。一個訊號準位,在很短的時間內,突然地,被改變訊號準位的電壓值,稱之為瞬間凸起雜訊(Noise Spikes)。有時也稱為”Glitch”。中文翻譯為,短暫的電磁波干擾、短時脈衝波干擾或稱低頻干擾。

上下限設定,或稱條件設定(Limit Settings)。PMU在量測電壓及電流時,會有上限值與下限值的設定。設定時,可以單獨設上限值,或下限值。也可以同時設定。測試機利用上下限值,來決定量測的結果,是否為Pass或是Fail。大部份的精密量測單元,都有電壓及電流的限制設定(Clamp Settings)。例如:電流有『限流設定』,電壓有『限壓設定』。限制設定,是一種硬體電路的設計。一般會在測試程式中使用。在量測過程中,限制設定是用來防止量到極大電流或極大電壓,而導致測試人員、測試硬體或待測物,因過大的電壓或電流,遭受到傷害或損害。

供應及量測模式(Force and Measurement Mode)。在測試領域裡,Force這個專有名詞,是供應電壓(Force Voltage)或供應電流(Force Current)的意思。當使用PMU時,不是供應電壓,就是供應電流。如果,在設定供應電流時,量測模式,會自動切換到量測電壓模式。相反地,設定為供應電壓時,量測模式會自動切換到量測電流模式。一旦Force Function被選定後,Force Range Settings就要被設定。

供應線及感應線(Force Lines and Sense Lines)。對PMU而言,為了供應更精確的電壓值,四線式電路設計(Four Wire System),通常會被採用。所謂的四線式電路設計(Four Wires System),是用兩條供應線(Force lines)來承載電流,用兩條感應線(Sense Lines),來量測電壓值。歐姆定律,用來說明電壓降的形成。是電流流經一個具某一電阻值的物體後 所產生的電位差。因為,線路本身皆具備電阻特性。因此,PMU供應的電壓值,與實際上供應到待測物的電壓值,是會有差異的。 當PMU被設定為供應電壓模式時,電流的限流設定(Current Clamp),就必須要設定。相反地,當PMU被設定為供應電流模式時,電壓的限壓設定(Voltage Clamp)就必須要設定。如果,某一待測物的接腳,與接地腳短路時,供應電流單元會持續增加電流,來滿足電壓值的設定。這樣的結果,會形成很大的電流。此電流,會流經待測物的接腳,並燒毀Probe Card、Circuit Traces、Pin Electronics Components、Fingers等等。

限制設定值(Clamp Settings),要比上下限設定值,或稱條件設定值(Limit Settings)的範圍大。舉例說明,PMU供應5伏特電壓,跨接於250歐姆負載上。在實際的量測中,待測物如同一個電阻性負載。從歐姆定律得知,電壓5伏特,電阻250歐姆時,其電流為20毫安培(mA)。IC規格書中,可能會說明,最大可接受電流值為25mA。因此,判定為Fail的電流設定值,要大於25mA。並且限流設定值(Current Clamp)為30mA。要特別注意的是,限制設定值(Clamp Settings),要設定在上下限設定,或條件設定值(Limit Settings)的外面,否則測試程式,永遠無法判斷為Fail。

當PMU被設定為供應電流模式時,限壓設定,就一定要設定。否則待測Pin是Open的情況時,所量測到的電壓值,很可能會很大。且大到足以損害、測試機或相關的人員。用此方法作量測時,期望量測到的電壓值,是在某一個事前定義的範圍內。如果待測物是失效的,其量測到的電壓值,可能遠大於期望值。為了要確認PMU所供應的電壓,會在規格書中,可接受的電壓值為5.25伏特時,Fail Limit可設為大於5.25伏特。同時Voltage Clamp,可設定為6伏特。

接腳電子電路介面(Pin Electronics)。通常用英文稱呼,會比較順口。一般稱Pin Card、PE Card、PEC或I/O Card。它是一種硬體介面,介於測試機與待測物之間的設備。它主要的功能是,供應輸入訊號到待測物的輸入腳上。並且從待測物的輸出腳,接收輸出訊號。每一種測試系統,對Pin Card而言,有它自己獨特的設計。但一般,會包括以下幾點特性(1)驅動電路,以便供應輸入訊號。(2)具備I/O切換開關。如驅動電路開關、電流負載開關。(3)電壓比較電路,以便偵測輸出電壓準位。(4)PMU的連接點。(5)可程式的電流負載。(6)高速電流量測單元選項。(7)Per Pin PMU選項。雖然有各種不同的設計,圖2-3是一種典型的單一測試通道(Single Channel)的PE Card設計。

驅動電路(Driver)。驅動電路,會接受來自高速子系統電路,且被格式化的訊號。此訊號,一般被稱為FDATA。當訊號,經過此驅動電路時,驅動電路將參考電壓供應器所供應的VIH/VIL電壓作比較,並且將此電壓加入FDATA中。舉例來說,FDATA 中的訊息,是要驅動邏輯0的電壓到待測腳時,驅動電路會依此指示,將VIL電壓值驅動到待測腳上。在此,重複解釋VIL電壓值的意義。對輸入腳而言,VIL(Input Voltage in Low)的意義是,當邏輯值為零時的最大電壓值。相同地,VIH電壓驅動等同 VIL電壓驅動。當測試通道(Tester Channel),被設定為輸入通道(Driver Pin/Driver Channel)時,驅動電路前端,與待測腳之間的開關(F1)會連通。並且K1的開關也會連通(參閱圖2-3)。如此訊號可以藉由驅動電路,傳送的待測物的接腳上。相反地,當測試通道(Tester Channel)被設定為輸出通道(Output Pin/Compare Pin / Compare Channel),或者是 “Don’t Care” 時,驅動電路前端與待測腳之間的開關(F1) 不會連通。如此一來,訊號就無法藉由驅動電路,傳送到待測物的接腳上。編號F1,是一種的場效電晶體(Field Effect Transistor),被用來當成一種高速的切換開關。並且,用來區隔驅動電路與待測物。也就是說,待測物,會從測試機讀取資料,或者提供資料給測試機。這個時候,高速切換開關,扮演重要的角色。簡單的說,當測試通道(Test Channel),設定為輸入通道(Input Channel),或驅動通道(Driver Channel)時,F1開關是在連接的狀態(On)。如果,是設定為輸出通道 (Output Channel),或比較通道(Compare Channel)時,F1開關,是在不連接的狀態(Off)。這樣的設計,是很重要的。因為,它可以確保待測物與驅動電路,不會同時,做電壓的驅動。這種現象,英文稱為I/O conflict 或者稱為 Bus contention。

電流負載(Current Loads),可以稱為動態負載(Dynamic Loads)、可程式化電流負載(Programmable Current Loads)或稱活動(Active Load)。它所扮演的角色,是在功能測試項目的過程中,加上負載到待測物輸出腳上。此負載,可以是正電流負載或負電流負載。所謂正電流負載,其電流方向是由測試機流向待測物。負電流負載則是待測物流向測試機的方向。動態負載,可以提供IOH(Output Current in High)電流及IOL(Output Current in Low)電流。IOH電流值,為輸出腳在邏輯1時的電流值,其方向為流入待測物的方向。IOL電流值,為輸出腳為邏輯0時的電流值,其方向為流出待測物。測試程式設定好 IOL/IOH電流值後,必需設定VREF電壓值。此電壓值的設定,是用來做IOL/IOH電流負載的開關切換點。當輸出腳的電壓小於(more negative)於VREF電壓值時,形成一個IOL電流負載。相反地,當輸出腳的電壓大於(more positive)於VREF 電壓值時,形成一個IOH電流負載。通常,電流負載的使用時機,做功能測試時的Tri-State測試項目中會用到。或者是用Pattern的方式測 OPEN/SHORT時會用到。F2也是一種場效電晶體,當成一種高速切換開關來用。當Channel為驅動模式時,F2為關閉狀況(OFF),動態負載電路不會連接到Channel上。當Channel為輸出模式時,F2為開啟狀況(ON),動態負載電路,會連接到Channel上。

電壓比較器(Voltage Comparator)。電壓比較器,通常是在功能測試時,被用來比較輸出腳的電壓值與RVS提供的參考電壓值。如果輸出腳的電壓值,等於或小於VOL時,其值被認定為邏輯0。如果輸出腳的電壓,等於或大於VOH時,其值被認定為邏輯1。如果其電壓值,介於VOL與VOH之間時,稱為Tri-State Level或稱為Bad Output。

高精密量測單元的連接(PMU Connection)。當PMU需要連接到測試接腳時。首先K1繼電器,會先打開(Open)形成斷路。接著K2繼電器會關閉(Close),將PMU連接到測試接腳上。

高速電流比較器(High Speed Current Comparator)。某些測試系統,除了利用PMU快速地量測小電流,或者採用高速電流比較器來量測。電流比較器,通常被用來做高速度的漏電流量測。當需要用電流比較器量測時, K3繼電器,會關閉(Close),將電流比較器,連接到待測接腳上。一般量測微量電流時,會先將電流轉換成電壓再量測。此種量測方式,可以在一個操作週期內,完成量測的動作。其速度,比一般的比較器快上10的6次方倍,因此,稱為高速電流比較器。Per Pin 高精密度量測單元(PPPMU)。同時間內,具備多腳量測電壓或電流的量測設備。其基本功能與PMU相同。

測試系統的種類

測試機或測試系統,英文稱為 Automated Test Equipment(簡稱ATE)。雖然測試機在設計上,會考慮通用性。也就是說,不因 Device 種類的差異,而皆能達到測試的要求,但這樣的考量,會使得測試機的設計,更加地複雜與困難,且其效率並不顯著。因此,大部份的測試系統,會針對 Device 的種類,作比較特殊的設計,來滿足因 Device 本身的特殊需求。測試機的分類,也因此區分為記憶體測試機(Memory Tester)、類比訊號測試機(Analog Tester)、混合訊號測試機(Mixed Signal Tester)、數位訊號測試機(Digital Tester/Logic Tester)。以下,逐一針對這些類別的測試系統,作簡單的介紹。

記憶體測試機(Memory Tester)

記憶體測試機,比較像數位訊號測試機。尤其,在直流參數的量測,是一樣的。一般在記憶體測試機的功能要求上,是希望能提供獨特的測試向量(Function Pattern)。這些Pattern或稱Test Vectors,是不會事先存放在測試機本身的Vector Memory內。而是透過專屬電路所產生出來的,此電路稱為Algorithmic Pattern Generator(簡稱APG)。一般典型的記憶體測試向量,有以下幾種Check board, Inverted Check board, Walking Ones, Walking Zeros, Butterfly及March Pattern等。這些Pattern 名稱,在此我沒有把它翻成中文,直接用英文稱呼它,會比較順口。一旦記憶體測試機,需要用到這些Pattern時,會透過APG電路來產生,而不像非記憶體測試機,須要事先將Pattern存放於Vector Memory內。記憶體測試機,還有一項特性是,測試的過程,需要較長的測試時間。因此,大部份利用平行測試的方法(同時測多顆的方式),來減少測試時間。

類比訊號測試機(Analog Tester)

一般類比訊號測試機,在量測的過程當中,對電壓與電流的量測,需要較高的精密度。有時候,所要求的級數,會在微伏特(Micro Volts)或 Pico Amps。類比訊號測試機,在直流參數的量測,與數位訊號測試機的直流參數量測,是不相同的。它須要比較特殊的儀器,作類比參數的驗證。因為,每一種Device,都會有特殊的需求。所以,類比訊號測試機在設計上,大多採用積架的組合方式,來滿足各種 Device 的需求。

混合訊號測試機(Mixed Signal Tester)

混合訊號測試機。顧名思義,它需要俱備數位與類比的測試能力。一般,有所謂的(大D小A)或(小D大A)。大D小A型式的測試系統,主要用來測試數位電路為主。其應用於直流參數測試與功能測試,是很有效率的。但,它只能作很少部份的類比參數量測。相反地,小D大A,是針對類比電路為主。它可以很精確量測類比參數,但對功能測試,是很有限的。

數位訊號測試機(Digital Tester)

一般數位訊號測試機,在價格上是比較高的,效能相對比較好。體積會大得多,功能選項上,有較多的選擇。當然,這種系統桌上型式的也有,但成本比較低,相對功能也比較有限。比較適合用於腳數(Pin Count)較少,複雜度較低的Device。一般而言,這種測試機的最高速度為20MHz,其Pattern Memory也比較小。所以,比較適合SSI或MSI的 Device。

高階的數位訊號測試機,Pin Count數較多,且頻率較高。其頻率可到400MHz以上。測試通道數(Test Channels),可到1024 Pins以上。並俱備高精密的時序電路。其測試向量,可存放百萬以上的Pattern。通常,新的IC會用高階的數位訊號測試機,作特性分析。當然,也有比較中等的測試系統。通常,為了成本的控制,選擇適當的測試機,來滿足 Device 在測試上的需要,是很重要的關鍵。選對了,您的測試成本,就可以節省下來!否則….

測試準則

以下的規則,適合大多數的例子。在許多的測試程式裡,這些問題,是一再地發生。您應該曾經想要規避這些錯誤,並想確認及了解所有問題的結果。有些規則,似乎很明顯。這些規則,建立在高精密的測試機時,它比你想像地容易。

準則一

如果它是一支輸出腳時,在功能測試時,絕對不要把它當成輸入腳。這種狀況,通常會在一種偶然的情況發生,尤其,在設定輸出遮罩時,不小心被設定成輸入腳。請記住,在功能測試時,輸入腳是無法拿來測試為PASS或FAIL。此外,訊號是藉由輸入腳提供給電路使用,而輸出腳的訊號是用來比較之用。

準則二

絕對不要將測試機的驅動電路(Driver Channel),連接到待測物的輸出腳上。這樣的結果,會導致測試系統和待測物接腳,在同一時間及同一接點上,驅動相同的電流與電壓值。

準則三

不要將輸入腳浮接(Floating)。一個合法的邏輯0,或邏輯1的準位電壓,必須要供應到輸入腳上。一般CMOS電路,如果輸入腳浮接的話,會產生閂鎖現象(Latch-up)。SCR效應,會引起瞬間的大電流,而損害待測物的本體。

準則四

絕對不要供應一個大於VDD的電壓值,或小於接地點的電壓值,到輸入腳或輸出腳上。這樣的動作,可能會讓CMOS 電路形成閂鎖現象(Latch-up)。

準則五

測試機供應電壓時,請記得設定限流措施(Current Clamp)。

準則六

測試機供應電流時,請記得設定限壓措施(Voltage Clamp)。

準則七

當測試機連接到待測物的接腳上時,絕對不要去改變供應的電壓值,或電流值。也絕對不要企圖去改變供應的模式。