第一章 – 電子學基本概念

電壓(Voltage)其單位為伏特(符號以V來表示)

電流(Current)其單位為安培(符號以A來表示)

電阻(Resistance)其單位為歐姆(符號以Ω來表示)

歐姆定律

歐姆定律是電學的基本定律

公式為 V = I * R。V是電壓、I是電流、R是電阻。因此,當其中兩者已知時,即可求得其中一個未知

基本量測方法

通常測試系統,會提供電壓來量電流,或者提供電流來量電壓。測試系統通常不會直接量測電阻值,而是經由量測電壓或電流,再利用歐姆定律計算出電阻值。以下介紹這兩種測量電阻的方法:

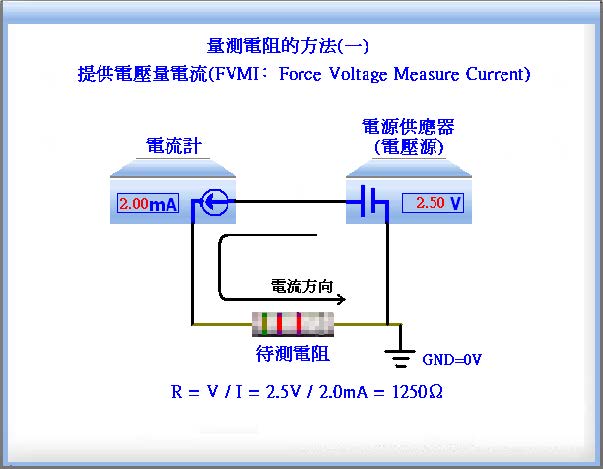

方法一:提供電壓量電流(FVMI: Force Voltage Measure Current)

此方法是,給予一個已知2.5V伏特電壓後,利用電流計與待測物串連來量測電流值。量測後再利用 R=V/I 公式,計算出電阻值。使用此方法,量測電流值的過程中,要注意,當電阻R很小時(趨近於零),電流I的值會很大。如此會導致電流計燒毀,或待測物損壞。因此,一般情況下,需作電流的限流措施(Current Clamp)。

R = V / I = 2.5V / 2.0mA = 1250Ω

一般在測試的過程中,會依IC設計的規格來確認。如果電阻的規格為 1250Ω±10%,則電阻最小值為1125Ω(= 1250Ω -1250Ω*10%)。當電阻值為1125Ω時,電流值為2.2mA。當電阻為1375Ω時,電流值為1.8mA。因此,電流的限流設定(Current Clamp),會設為2.2mA。所以,所量測出的最大電流值,不會大於2.2mA。

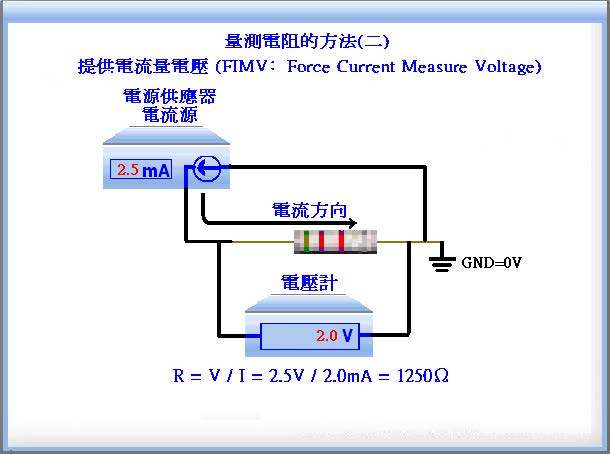

方法二:提供電流量電壓 (FIMV: Force Current Measure Voltage)

此方法是,給予一個已知電流I。電壓計跨接電阻兩端後,量測電壓值(與待測物並聯)。再利用 R=V/I 公式,計算出電阻值。使用此方法,量測電壓值的過程中,要注意,當未知的電阻

R趨近於無限大時,所量測出的電壓值會很大。此結果,會導致電壓計燒毀或待測物損壞。為防止上述情形的發生,一般會作電壓值的限壓措施(Voltage Clamp),設定好最大的電壓值。

最大電壓值 V = I * R = 2.50mA * 1375Ω = 2.75V。

最小電壓值 V = I * R = 2.50mA * 1125Ω = 2.25V。

因此,電壓的限壓設定值,會設在2.75伏特電壓。

數位邏輯

積體電路在設計上,有兩種較被廣泛使用的技術。TTL (Transistor -Transistor Logic)和CMOS (Complementary Metal-Oxide Semiconductor)這兩種技術。TTL電路的執行速度比CMOS電路快,但消耗能量較高。CMOS的能量消耗與其頻率有關。較高的運作頻率,會有較多的能量消耗。TTL電路,則是固定的能量消耗。然而以目前而言,CMOS電路設計,是比較被廣泛使用的一種技術。

電壓值代表邏輯準位

一般邏輯電路中,會以高電位代表邏輯1,而以低電位來代表邏輯0。邏輯電路的資料讀取與寫入,是以邏輯準位為基準。邏輯準位的定義,由電壓值來決定。例如:大於1.8V的電壓值,定義為邏輯1,而小於0.4V的電壓值,定義為邏輯0。

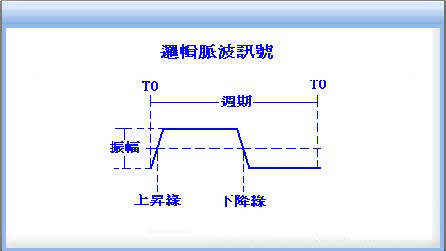

邏輯脈波訊號(Logic Pulse)

週期(Period) = 1 / 頻率( Frequency)

頻率( Frequency)=200MHz 則週期(Period)=5nSec。

週期(Period)一般英文稱為 Cycle。

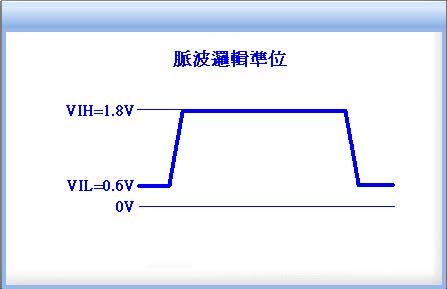

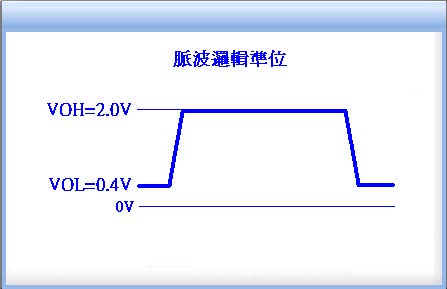

脈波訊號準位 (Pulse Level)

圖: 輸入訊號 (Input Pulse)

輸入電壓為1.8V以上時,稱為邏輯1。VIH ( Input Voltage in High )=1.8V。

輸入電壓為0.6V以下時,稱為邏輯0。VIL ( Input Voltage in Low )=0.6V。

圖: 輸出訊號 (Output Pulse)

輸出電壓為2.0V以上時,稱為邏輯1。VOH(Output Voltage in High)=2.0V。

輸出電壓為0.4V以下時,稱為邏輯0。VOL(Output Voltage in Low )=0.4V。

基本數位邏輯閘

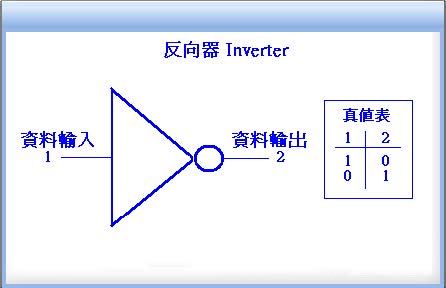

Inverter 反向器

反向器,是一個最基本的邏輯電路。具備一支輸入腳(Input Pin)及一支輸出腳(Output Pin),它主要功能,是將邏輯1的值改變為邏輯0的值。

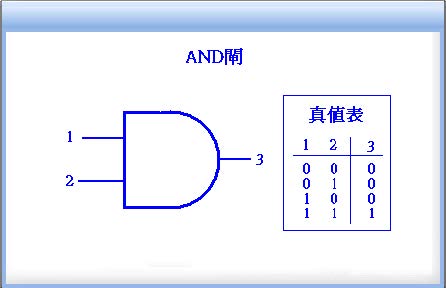

AND閘

AND閘的主要功能,其輸出腳的邏輯值,是依所有輸入腳的邏輯值而定。當所有輸入腳的邏輯值為1時,則其輸出腳的邏輯值為1。同時,當有一支輸入腳的邏輯值為0時,其輸出腳的邏輯值則為0。其輸入腳數量可以2支以上,也可以只有一支輸入腳。一般而言,利用基本邏輯閘,所組合設計而成的電路(例如利用AND、OR閘等),稱為邏輯電路。

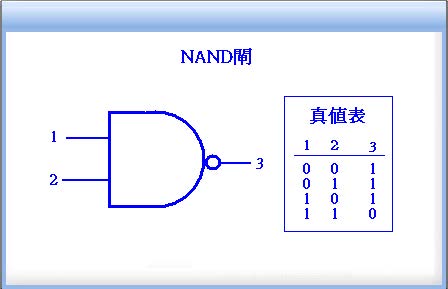

NAND 閘

當所有輸入腳的邏輯值為1時,則其輸出腳的邏輯值為0。同時,當任何一支輸入腳的邏輯值為0時,其輸出腳的邏輯值則為1。其輸入腳數量,可以2支以上,也可以只有一支輸入腳。NAND閘的功能,如同AND閘後加上一個反向器。它之所以存在的主要原因是,在半導體的製造過程中NAND閘比AND閘容易製作。並且,它時常用來優化邏輯電路,降低邏輯閘的數量。

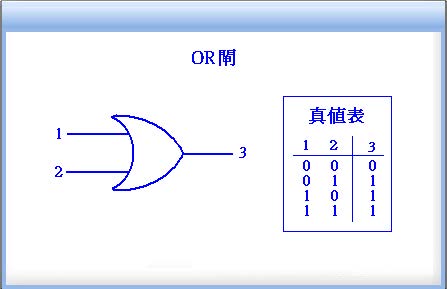

OR 閘

當所有輸入腳的邏輯值為0時,則其輸出腳的邏輯值為0。同時,當任何一支輸入腳的邏輯值為1時,其輸出腳的邏輯值則為1。其輸入腳數量,可以2支以上,也可以只有一支輸入腳。

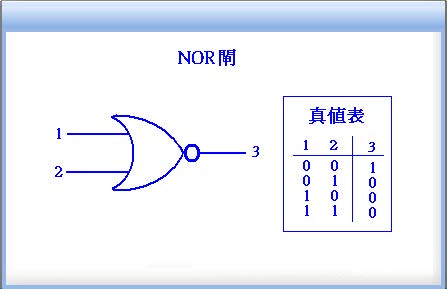

NOR 閘

當所有輸入腳的邏輯值為0時,則其輸出腳的邏輯值為1。同時,當任何一支輸入腳的邏輯值為1時,其輸出腳的邏輯值則為0。其輸入腳數量,可以2支以上,也可以只有一支輸入腳。

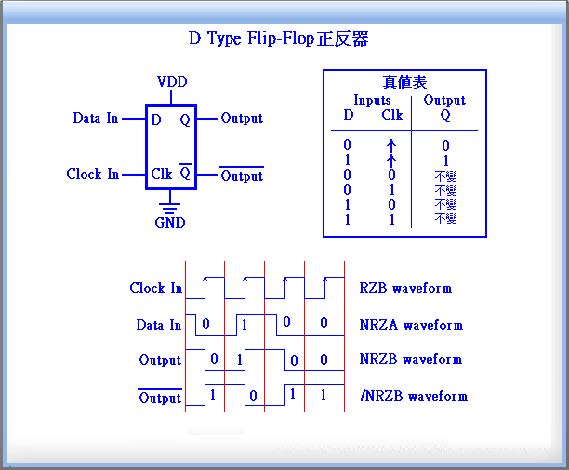

D Flip-Flop閘

正反器(Flip Flop)。之所以如此命名的原因,是當時脈訊號(Clock Signal)輸入時,其輸出腳的邏輯值會改變。Flip的中文意義為輕輕彈起揮動的意思。Flop的中文意義為拍動搖晃如拍翅膀一樣。也就是說透過時脈訊號的輸入,讓輸出腳的值,如拍動翅膀一樣迅速地改變。輸出腳邏輯值的觸發方式,一般有兩種。一種是準位觸發(Level Triggered),另一種是邊緣觸發(Edge Triggered)。一般最常用,且最有用的方式是邊緣觸發(Edge Triggered)。所謂觸發(Trigger)的意義是,當時脈訊號輸入時,或者時脈訊號準位發生變化的那一殺那,輸出腳的邏輯值,才會改變。邊緣觸發,又可分為正向上昇邊緣觸發 (Positive Raising Edge Triggered)及反向下降邊緣觸發(Negative Falling Edge Triggered)。以正向上昇邊緣觸發 (Positive Raising Edge Triggered)為例。當時脈訊號(Clock Signal),由邏輯0改變為邏輯1時的那一霎那,輸出腳才作改變。Flip Flop正反器,具備單一資料輸入腳或多支資料輸入腳,及一支時脈輸入腳,一支資料輸出腳。有些正反器,可能會加上一些其它功能的腳位。例如 Preset輸入腳、Clear輸入腳或反向資料輸出腳(/Q)。

圖: 所示的D Type Flip-Flop,有一支資料輸入腳(Data in)及一支時脈訊號輸入腳(Clock In)。還有一支正向資料輸出腳,及一支反向資料輸出腳。”D”的意義

為 Output duplicates the input after a clock edge triggers it。在時脈訊號正向上昇邊緣觸發之後,複製輸入腳的邏輯電壓值到輸出腳。由以上說明,D Type Flip Flop,可以被當成一個記憶體單元。因為輸出腳,會一直記憶現在的邏輯值,直到下一個觸發訊號的來臨。下一個觸發訊號的來臨,才會改變輸出腳的邏輯值。這樣的特性,如同一個記憶體單元。正反器還有其它型式,如T Type 及 J-K Type等等。

這一章節,用以上簡單的介紹,引導第一次學習的工程師,進入半導體測試的領域。這樣的內容,並不能涵蓋學習半導體測試,所有應具備的基本知識。例如:BJT電晶體,MOSFET電晶體,及電子電路的基本原理。這些需要工程師們,自行自修與自我學習,在往後的學習過程中,會有無比的助益。