第九章 – 開發測試向量

測試向量

測試向量(Test Vectors)也可以稱為測試圖樣(Test Patterns),或是真值表(Truth Tables)。測試向量的內容,代表輸入腳與輸出腳的邏輯狀態。這些邏輯狀態,是設計者要求待測電路應執行的功能。而輸入腳與輸出腳的狀態,是用某個英文字母、數字、或符號來表示。例如1/0通常用來代表輸入腳的狀態。L/H/Z通常用來代表輸出腳的狀態。而X字母,對輸入腳而言,代表不做輸入驅動。對輸出腳而言,代表不做比較動作。任何的英文字母、數字、或符號,都可以用來代表輸入腳與輸出腳的狀態。只要測試系統能夠定義,且正確地執行應有的功能即可。

測試向量會依序地被儲存在測試向量記憶體(Test Vector Memory)當中,並且每一行(Raw)測試向量,會在一個測試週期內被執行。除了從測試向量記憶體而來的訊息之外,還包括時序(Timing)、波形(Waveform)、電壓準位(Voltage Level)等。這些訊息,會藉由測試系統的Pin Electronics Card的驅動電路,送到待測物的接腳上。另外,待測物輸出腳上的訊號,會藉由Pin Electronics Card的比較電路來做比較。它的比較對象,也是事先儲存在測試向量記憶體當中,且比對的時間(Strobe Time),是我們預先設定上去的。以上所描述的測試方式,被稱做儲存與反應(Store and Response) 的測試方法。因為,期望的資料,事先已經被儲存在測試向量記憶體當中。

測試向量,除了包括待測物的狀態之外,還包括測試機的測試向量微指令。舉例來說,測試向量可能在執行過程中,想要變更時序設定(Change on the Fly)。這個意思是,訊號的時序及訊號的波形,可以以一列為單位來設定與執行。而輸入腳的驅動電路,依需要可以開,也可以關。而輸出腳的比較電路,也可以以一個週期為單位來使用。許多的測試系統,通常會支援一些測試向量微指令。例如,分岐指令、迴圈指令、向量重複指令、子測試向量等等。這些微指令,會同時出現在測試向量檔內。然而不同的測試系統,會有不同的測試向量微指令。當測試程式從一種測試系統,轉移到另一種系統時,測試向量需要做轉換是其中的一項理由。

對於複雜的待測物而言,其測試向量通常會在設計的過程中,由模擬的資料中萃取出來。而這些模擬的測試資料,通常會針對不同的測試平台,做格式的轉換。通常此測試向量檔案,會包括數百萬以上的測試週期。這些模擬的測試資料,可以由設計者來產生,也可以由測試人員,或模擬人員來產生。要能夠產生正確的測試向量,其重點在於完全瞭解待測物的特性,及測試系統的功能,才能達成目標。

■ 測試向量檔的範例

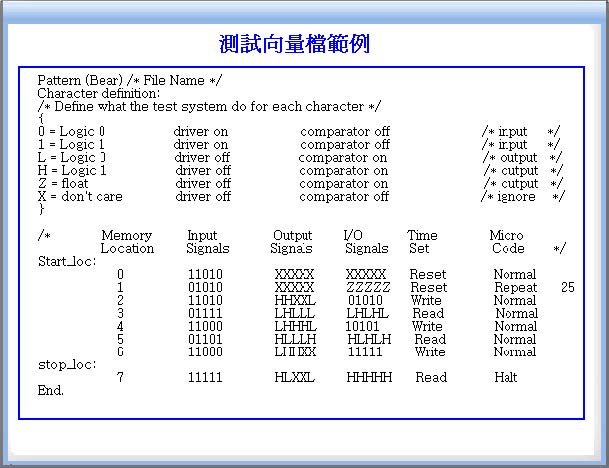

圖1所示,是一種典型的測試向量檔。它一開頭先定義測試向量的名稱,及在測試向量檔內所使用的每一個向量字母。這個檔案用了三個時序(Time Sets)。這三個時序設定分別為,重置(Reset)、寫入(Write)、讀取(Read)。而時序的設定值,並沒有出現在測試向量檔案內。而主測試程式,會根據每一個時序名稱,定義時序的設定值。而測試向量檔案內,會定義你要使用的是哪一個時序名稱。有些測試系統,可以支援使用時序名稱的做法。而有些測試系統,只支援使用時序名稱的編號。

注意,I/O訊號腳可以使用所有的向量字元。例如,輸入腳的(0/1),輸出腳的(L/H),三態腳的(Z),或者忽略不處理的(X)。而微指令是額外對測試向量做控制的命令。在這個範例中,「Normal」這個微指令,表示這行測試向量,以一個測試週期的時間來執行。「Repeat 25」這個微指令,表示這行測試向量,被重複執行25次(或稱25個週期)。「Halt」這個微指令,表示中止測試向量的執行,並停在這行測試向量。因此微指令,對測試向量而言,可以增加相當大的彈性與能力。然而,他們屬於程式語言的一部份,並隨測試平台而異。

圖9-1

設計人員是最了解電路的人員,通常也會是測試向量的製造者。而測試人員應僅早參與計劃,並與設計人員討論測試相關細節。例如,時序的設定,電壓的需求,測試向量的深度,及如何產生測試向量等等的問題。提供一份測試向量微指令給設計人員。如果需要的話,向它們解釋測試平台上,可用到的測試資源,及測試平台的限制。

現今大部份的設計人員,需要相當多的測試向量,來驗證電路。而這些測試向量,是很少能用人工來完成的。如果你必須要用人工的方式來產生測試向量的話,請找出一種自動處理的方法。例如,使用巨集來產生測試向量,或者是用C或Pascal電腦語言,來開發測試向量。並將電路的功能,做功能區塊的劃分,並將每一個區塊功能,開發成副程式。例如,Read/Write Bus,Reset,Read/WritePort,Send/Receive Data。

測試向量,是藉由測試平台內的高速測試向量記憶體來執行。記憶體的大小,就決定了能夠容納多少個測試向量檔。有些測試平台的記憶體深度只有4096。而有些測試系統會有1M以上的深度。如果測試過程中,需要重新載入測試向量到測試向量記憶體時,這樣的狀況下,一般會增加測試時間。因此,如果測試向量的大小,遠大於測試平台的記憶體大小,這樣的做法是不切實際的安排。

■ 測試向量範例

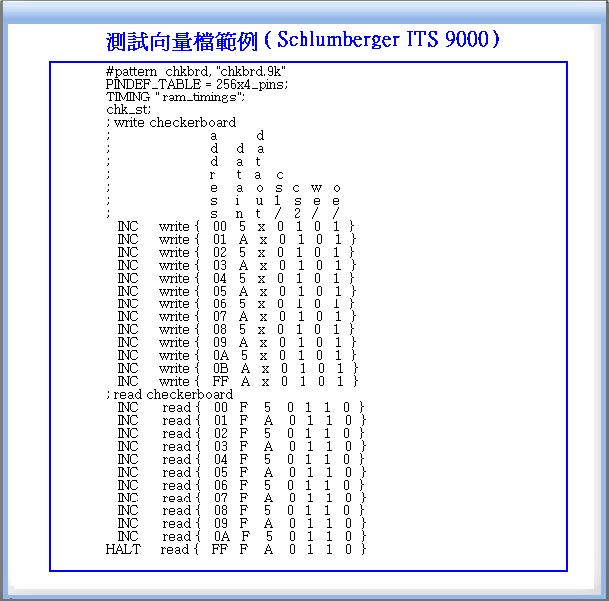

圖2是Schlumberger ITS9000測試系統的範例檔。它是一個Check Board的測試向量,用來測試 256X4 靜態記憶體之用。第1行代表地址匯流排,它用16進位的方式來表示。地址位置是由0到256的方式逐一遞增。這個範例,有些向量已被移除。第2行代表輸入的資料,它也是用16進位的方式來表示。注意,16進位的5及16進位的A,可以產生出Check Board的圖樣。第3行代表輸出資料,也是用16進位的方式來表示。如果在寫入週期中,資料輸出用「X」來表示時,代表輸出的訊號將不做測試。

在讀取週期中,資料輸出欄位中的5與A,也是用16進位的方式來表示。第4行與第5行,代表CS1及CS2/。第6行代表WE/。最後一行代表OE/。請注意「Read」「Write」代表時序設定組合(Timing Sets)。這個測試向量檔,用了兩個時序組合。「Write」時序組合中,包含時序設定及波型訊息,以便寫入資料到RAM當中。相同地,「Read」時序組合,包含時序設定及波型訊息,以便讀取RAM當中的資料。

■ 模擬用的測試資料

一旦電路設計完成,同時也完成模擬時。我們可以將模擬後的結果,儲存成文字檔案。這個檔案,稱為模擬測試資料檔(Simulation Data)。接下來,我們可以將此檔案轉換成,測試平台上可以執行的測試向量檔(Test Vector/Vector Data)。模擬測試資料檔,包含所有輸入/輸出狀態。同時,在每一行都會有一個時間戳記(Time Stamp Value)。

有兩種方法,用來抓取模擬測試資料檔。一種稱為觸發抓取(Print on Strobe)的方法,也可以稱為以週期為基礎的抓取方法(Cycle Base Capture)。這種方法,會在每一個測試週期內的特定時間點,記錄所有輸入腳與輸出腳的狀態。這種方法所抓到的模擬測試資料,其一列就代表一個測試週期。因為,抓取資料是在單一週期內的單一特定點上抓取。因此,在抓取的那個時間點之外的任何訊號的轉換將會遺失。但是,如果所有的訊號波形是NRZ的話,則不會有任何訊號的遺失。因為訊號只會在週期開始時做改變。

圖2

另一種方法為,當訊號改變時抓取(Print on Change)。也可以稱為以事件為基礎的抓取方法(Event Base Capture)。當任何訊號改變時,就產生一列模擬測試向量。一旦使用這種方法,將所有的訊號抓取後,會產生許多列的模擬測試向量。許多列的模擬測試向量,只代表一個測試週期。因此,這種方法所產生出來

的檔案,相對比較大。當模擬測試向量轉換成測試平台所使用的測試向量,其轉換的過程當中,會存在許多的問題。以下的模擬指引,或許會有所幫助。

模擬測試(Simulation for Test)

通常測試平台上,所需的測試向量,是由邏輯電路的模擬測試資料轉換而來,並且轉換的格式是測試平台所規定的格式。這段說明的目的,是提供一個指引,讓工程人員知道,如何做出模擬測試向量。並且,將它們轉成測試平台上,所需的測試向量。

■ 模擬指引(Simulation Guidelines)

1. 請確認在測試向量的一開始,是否對電路做完整的初值化動作。這個初值化的程序,不應該只有供電的程序而已。來自模擬資料的測試向量,當重複模擬時,應該要有一致性。每一個模擬資料檔案,都應該是獨立性的模組。也就是說,每一個模擬資料檔案,不需要其它額外檔案的輔助。

2. 在電路模擬的模式下,要達到電路初值化的目的,需經由一般的功能應用來達成。可能的話,可以使用「重置(Reset)」,這個功能。舉例而言,如果電路有一個正反器(Flip Flop),而這個正反器雖然無法被重置或初值化,但模擬資料檔案或許是正確的,且在應用上是可以運作的。無論如何,在這種狀況下,模擬資料檔案,可能會依實際電路啟動的狀態,而來決定是否可用。

3. 內部與外部節點(Node),不應事先自行預測在某一種狀態。節點狀態應該藉由模擬資料的初值化程序來確定。

4. 電路的輸出腳應該在電路完整初值化程序後,再開始對它做測試。即便某些輸出腳,我們都很清楚及都很肯定它的輸出狀態為何。

5. 對外部訊號而言,我們會建議使用,訊號改變時抓取(Print on Change)模式,來產生測試模擬資料。這樣子,我們可以很確定所有電晶體的訊號,都會被抓取到,且有助於後續的處理。

6. 要俱備一種方法,它可以用來辨識,各種訊號的狀態,它們包括輸出入訊號及三態訊號(Tri-State Signal)。這些訊號中,有些可能是提供內部電路使用的訊號。例如三態緩衝器的「致能(Enable)」訊號。如果,能夠很清楚地區別,各種訊號的狀態,則測試系統就能很清楚地,提供相對應的資源來達到測試的目的。例如,是否提供驅動電路、或是比較電路、還是忽略它。

7. 在模擬模式及測試模式下,所使用的頻率與時序條件都應該要相同。最好及最壞的情況,都應該要被模擬。這些狀況下的測試結果,都應該拿來比較。以便確認輸出訊號,沒有跨越週期邊界(Cycle Boundary)。

8. 當某一電路需要多重時脈訊號時,而多重時脈訊號是源自於相同頻率,或者是多重時脈訊號之間的倍數相乘關係。例如,測試機可以提供4MHz的頻率,並依此產生另一個8MHz的頻率。但沒辦法正確地提供4MHz及7MHz的時脈訊號頻率。

9. 雖然,在非同步狀態下,我們依然可以執行模擬。但大部份的數位系統,是同步的機台。因此,模擬出來的波形,在後續處理的過程中,必需要被切割成以週期為單位的測試向量。因此,我們必須要嘗試將模擬的輸入訊號,群組成以週期為單位的測試向量。

10. 如果可以的話,儘量避免使用不同時序(Time Set)的組合。在同一個測試向量中,如果使用不同的時序(Time Set),這種做法我們稱為「Timing Changes on the Fly」。

11. 如果我們想以16進位格式下,產生模擬測試向量。請在產生之前,請確認如此做不會引起其它的問題。有些轉換軟體,無法處理16進位格式。有時需要重新將16進位格式,轉換成2進位格式,才能處理。

12. 當我們需要做交流參數特性分析,來驗證設計規格時。這個時候,模擬時所用的時序,應該與規格書內容相同。舉例而言,當您在驗證設置時間(Setup Time),這個測試項目時,被量測的訊號及參考的訊號,都需要在相同的測試週期內。

13. 用測試向量來驗證直流參數(DC Parameter)的做法,是一種很有用的做法。舉例而言,動態IDD電流量測時,電路需要被確定在某一條件下才被執行。而此測試向量的目的,就是用來讓電路進入某種期望的狀態。其它直流參數驗證時,可能包括以下的條件來驗證。

- VOL/VOH – 所有的輸出狀態,必需要驅動成0或1的狀態。這種情況,可能是靜態或動態的測試結果。

- VIL/VIH –有的輸入狀態,必需要設定成0或1。

- 靜態IDD及動態IDD – 將電路設定成你想要的狀態。

- 三態腳(Tri-State) – 所有的雙向腳(Bi-Direction),及三態輸出腳都應該被驅動在高準位狀態。

14. 時序圖的繪製,是絕對必要的。所謂時序圖,是輸出入訊號之間的時間關係圖。

15. 如果你懷疑某些模擬測試資料會有問題,請與測試人員討論你所關心的問題。通常經過討論後,可以減少相當多的偵錯時間。如果可能的話,在開發模擬測試資料之前,請與測試人員討論一下相關的問題。如果時間已經太遲,你要將模擬測試資料的內容,告知測試人員。模擬測試資料使用到的測試向量字元,請特別將它整理並歸檔。