第七章 – 交流參數測試

交流參數測試的目的,是要保證所設計的電路,符合所有時序的規定(Timing Specification)。因此,在執行交流參數測試前,我們需要先對訊號的時序做一些設定。也就是決定每一根訊號的上昇緣,與下降緣的位置。同時,也要決定每一根訊號的波型(Waveform)。此波型,一般在交流參數規格表中,都會有定義。定義好時序之後,接下來,我們會執行一段測試向量(Test Vector),這段測試向量,會包括必要的邏輯功能,確保所有的交流參數,都能被測試與執行。

以下提出兩種方法,可以對電路的交流參數做驗證。第一種方法是將所有的交流時序參數,逐一設定在最差的狀態之下,再去執行功能測試向量。這是一種比較快速的方法,並且可以保證電路符合設計規格。無論如何,測試後,如果發生失效(Fail)時,就代表所設定的那一個參數,所引起的失效。

另一種方法,就是單獨性地測試交流參數。舉例來說,我們可以依規格書中的定義值,對Data Bus的設置時間(Setup Time)做設定,並放寬其它的參數條件。接下來,再執行測試向量。如果測試後的結果為失效(Fail),我們可以立即知道,這次引起失效的原因,是因為Data Bus的設置時間所引起的。這樣的方法,會持續進行到所有的交流參數都被驗證完畢。這種測試方法,可以提供更多且詳盡的訊息,對於提昇良率會有所幫助,但會增加了不少的測試時間。

各種測試方法

■ 「顯示並記錄」測試方法

將測試結果做顯示並記錄。這種測試方法,與測試的型態有關。一般而言如果對直流與交流參數做量測時,並且將結果列印在紙張上,或儲存在磁碟檔案中。這樣的方式,事後可以對電路的效能,做進一步的分析。通常,軍用規格的電路測試,需要用這種方法來測試。測試系統的記錄器及系統軟體工具,可以被用來提供這些訊息。

■ Go-NoGo測試方法

Go-NoGo測試方法,是不同於「顯示並記錄」的測試方法。Go-NoGo測試方法,是無法知道量測的數值。我們只能針對每一個測試參數,設定一個限制值。如果測試結果,是在限制值的範圍內,則為正確(Pass),否則為失效(Fail)。但量測值與限制值之間的差異(Margin)有多少,則無法得知。這種測試方法,大部份應用於量產測試。一般它的測試速度比「顯示並記錄」的測試方法要來得快。

■ 折衷辦法

電路規格書中規定的測試參數,不一定能夠在測試平台上實現。因此,當某些測試條件,無法在測試平台上實現時,我們必需提出折衷辦法,或者找到適當的測試設備來實現。以現今的電路而言(大部份是快速的電路),最大操作頻率這個測試項目(也稱為At Speed Test),是比較難實現的。我們通常會採用折衷的辦法。以下,舉一個折衷辦法的範例來說明。例如,最大操作頻率的量測,可以用輸入腳或輸出腳最差的時序設定來取代(注意,這不是最大操作頻率下的測試。測試系統在測試頻率這項要求上,通常無法滿足電路上的需求)。當我們如此做時,我們會將操作頻率,設定在比規格書定義的值還小,並且將一個或多個輸入腳或輸出腳的參數,依規格書的內容做設定,設定完成後,再進行驗證。循此方式,我們將驗證所有的時序參數,例如設置時間(Setup Time)、維持時間(Hold Time)、時脈寬度(Pulse Width)。輸出腳的遞延時間(Propagation Delay Time)也會被驗證。如此才能確保,電路的操作頻率,符合規格書中的規定。不在最大操作頻率下測試電路。這種做法,也可以說是單獨調整某一測試參數的做法,使得Device在最大速度下的效能,符合規格。

另一種折衷辦法,就是「多工測試」(Mux Testing)。多工測試,意味著以兩倍測試系統的速度,來測試待測物。有些時候,測試系統的測試頻率,會以下列方式來描述50/100MHz或100/200MHz。前面的數字,代表不打折扣的測試頻率(Uncompromised Test Frequency)。舉例而言,100/200MHz的測試系統,它的最小測試週期為10nSec,並在此速度下執行所有的功能。而第2個數字代表測試系統可以在200MHz的頻率下,提供資料訊號給待測物。在多工測試模式下,測試系統,會提供兩種輸入訊號。並且,在每一個測試週期中,測試兩個輸出訊號。所以待測物是以兩倍的測試系統頻率在測試。

多工測試,通常會有限制。會受限於時脈訊號的波型、測試向量記憶體的大小、輸出腳的訊號觸發位置(Output Strobe Placement)等等。測試速度(Test Rate)這個術語,隱含測試機的最大操作速率,而訊號速率(Data Rate),隱含待測物可執行的操作速度。如果需要的話,測試工程師的責任,就是找出折衷方案。而這個折衷辦法,要儘可能地延伸,並且保證電路符合規格。當折衷方案無可避免時,請與電路設計人員討論細節,或許他們會有一些辦法來解決這些事情。請確認並小心地將這些折衷辦法記錄並整理下來,並且與設計人員或相關人員確認。

標準交流參數

就如同直流參數一樣,我們也會討論一些標準的交流參數。接下來,讓我們來討論一下,最一般的交流參數。

■ 設置時間(Setup Time)

| Parameter | Description | Min | Max | Unit |

| tSD | Data Setup to Write End | 11 | nSec |

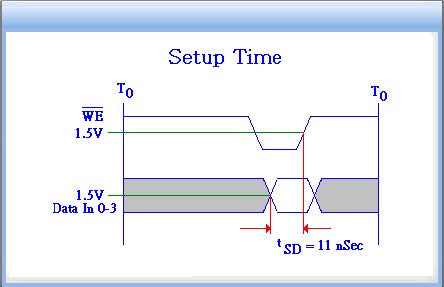

所謂的設置時間,是我們期待的訊號,應該要在參考訊號,到達某一個電壓準位之前,就要準備好的最小準備時間。如圖7-1所示,Data In這些訊號的設置時間,相對於WE(由低到高),且以1.5V這點電位為參考點,往前算的這段時間,它至少要有11nSec。

★設置時間,是要保證訊號在參考訊號前的最小時間內被讀取。

★只對輸入腳,做設置時間的量測。

★設置時間可能是負值。(因為它發生在參考訊號之後)。

★公式: Setup Time = Reference Signal – Result of Binary Search

圖1

■ 維持時間(Hold Time)

| Parameter | Description | Min | Max | Unit |

| tHD | Data Hold from Write End | 1 | | nSec |

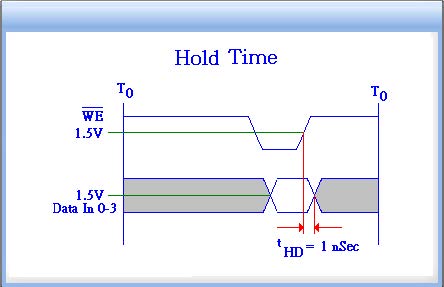

維持時間,是訊號在參考訊號到達某一個電壓準位之後,應該至少要維持一段時間。舉例而言,如圖7-2所示,Data In的維持時間,是由WE(由低到高)約在1.5V之後,所維持的這段時間,至少要有1nSec。

★維持時間,是要保證訊號在參考訊號出現之後,至少維持一段最小時間,以便能夠被讀取。

★只對輸入腳,做維持時間的量測。

★維持時間可能是負值。(它發生在參考訊號之前)。

★公式: Hold Time = Result of Binary Search – Reference Signal

圖2

■ 遞延時間(Propagation Delay Time)

| Parameter | Description | Min | Max | Unit |

| tAA | Address to Data Valid | 15 | nSec |

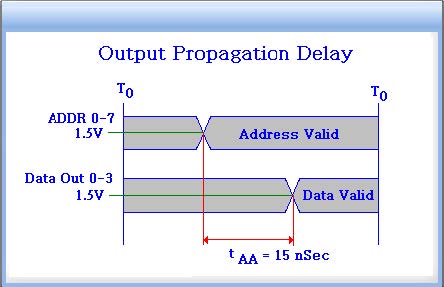

遞延時間是某一個訊號的轉換點,與另一個訊號的轉換點,這兩點間的時間差,我們稱之為遞延時間(Propagation Delay Time)。這個時間的量測,會在特定的電壓下做量測,通常是1.5V。而大部份遞延時間的量測,是從輸入訊號到輸出訊號之間的時間差。以圖7-3為例,地址訊號準備好的那個時間點,到輸出腳輸出訊號到達1.5V電壓時,這兩點的時間差,稱為遞延時間(Propagation Delay Time)。

圖3

有些時候,我們需要量測兩個輸出訊號之間的遞延時間。這樣的狀況下,我們需要在兩個輸出訊號之間,用搜尋的方法來量測它們之間的相關位置。輸出腳遞延時間的量測,也可以當成是「Critical Path Measurement」。

★遞延時間,是要保證訊號會在參考訊號的某一個電位出現之後的一段時間內出現。

★只對輸出腳,做遞延時間的量測。

★只會有正值。(因為,它發生在參考訊號之後)。

★公式: Prop_Delay_Time = Result of Binary Search – Reference Signal

■ 最小脈波寬度(Minimum Pulse Width)

| Parameter | Description | Min | Max | Unit |

| tWL | Minimum Clock Low Time | 20 | nSec | |

| tWH | Minimum Clock High Time | 25 | nSec |

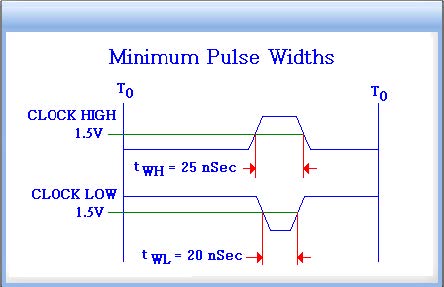

通常脈波寬度有兩種獨立的參數:

Minimum Clock Low Time:脈波維持在低電位的最少時間。

Minimum Clock High Time: 脈波維持在高電位的最少時間。

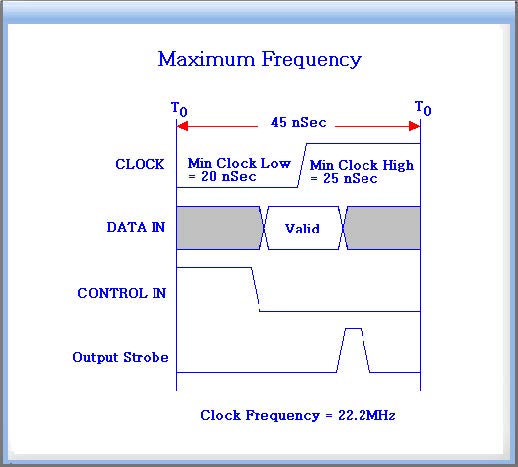

如果我們要對此參數做量測時,我們可以移動或調整訊號邊緣。同時還要確認所有的時序設定,仍維持與時脈訊號之間的關係。圖4說明,這兩個參數的意義。

★要保證脈波寬度維持在最小值。

★當控制訊號的邊緣改變時,要確認所有的訊號,仍維持與時脈訊號之間的關係。

圖4

■ 最大操作頻率(Maximum Frequency)

| Parameter | Description | Min | Max | Unit |

| fMAX | Maximum Clock Frequency | | 22.2 | MHz |

最大操作頻率(Maximum Frequency)測試,有時候稱為「速度測試」。也就是依規格書中所定義的最大速度來執行功能測試。這項測試,通常執行上是比較困難的。因為,會對待測物的所有時序做最差的時序設定。而這樣的設定,會導致測試雜訊的增加。這個雜訊,會引起待測物失效。在實現速度測試時,我們會在最大的操作頻率下,測試最差狀況的設置時間、維持時間、最小脈波寬度、及最差狀況的遞延時間。請小心細讀規格書,並確認所有時序的設定,都是正確的。

圖5

當執行任何的測試項目時,如果要移動或調整控制訊號的邊緣(Control Edge)時,例如時脈訊號,請確認,與時脈訊號有關的時序設定值,是否仍維持正確的設定值。例如,設置時間、維持時間、遞延時間等。如圖5所示。

★保證待測物可以操作在最大頻率之下。

★當控制訊號的邊緣改變時,要確認所有的訊號,仍維持與時脈訊號之間的關係。

★在做最大操作頻率測試項目時,通常會引起雜訊(尤其因測試所引起的雜訊)。

7-8

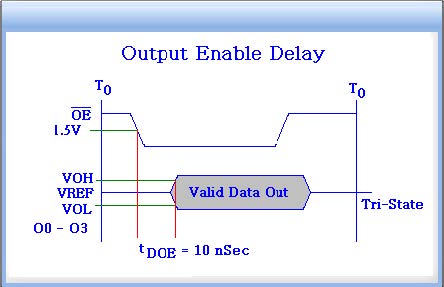

■ 輸出致能時間(Output Enable Time)

| Parameter | Description | Min | Max | Unit |

| tDOE | OE Low to Data Valid | | 10 | nSec |

圖6

輸出致能時間的計算,是參考訊號的某一參考電位開始,從那一點起算,到輸出訊號由高阻抗狀態,切換到邏輯準位狀態的這段時間。舉例而言,這段時間,是從DOEtOE訊號,由高電位變成低電位時,開始起算,直到O0-O3的輸出訊號出現的那一個時間點,這段時間我們稱為。 DOEt

這項測試,需要將輸出腳連接一個輸出負載電路,這個負載電路的參考電位為2.0V。在大部份的情況下,我們所定義的合法邏輯準位電壓為VOL / VOH。要確認這些值的正確性,請參考規格書中的定義。如圖7-6所示。

★要確保俱備高阻抗輸出緩衝器,可以從高阻抗狀態,轉換到期望的邏輯準位狀態,並且期待邏輯輸出腳,能夠在特定的一段時間內間(最多),能夠送出正確的訊號。

★只針對俱備高阻抗的輸出腳及雙向腳做量測。

★當使用二元搜尋法時,測試結果只會是正值。

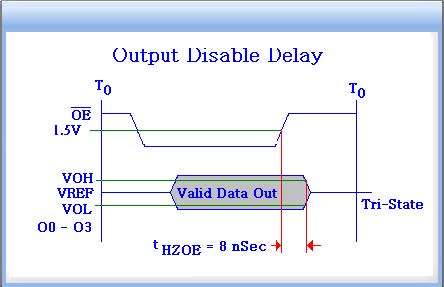

■ 輸出失能時間(Output Disable Time)

| Parameter | Description | Min | Max | Unit |

| tHZOE | OE High to Data High Z | | 8 | nSec |

圖7

輸出失能時間的計算,是參考訊號的某一參考電位開始,從那一點起算,到輸出訊號由邏輯準位狀態,切換到高阻抗狀態的這段時間。舉例而言,這段時間,是從OE訊號,由低電位變成高電位時,開始起算,直到輸出訊號,變成高阻抗狀態,這段時間我們稱為HZOEt。如圖7所示。

以此例而言,高阻抗狀態為不合法的邏輯準位。也就是此電壓大於VOL且小於VOH。且輸出腳必需連接一個輸出負載電路,此電路的參考電壓為2.0V。一旦待測物的輸出訊號關閉時,連接輸出負載電路上的結點,會因為輸出負載電路的關係,被拉到某一個不合法的電壓值(中間的某一個電位)。請依規格書中的規定驗證之。

★要確保俱備高阻抗輸出緩衝器,可以在某段時間內,由邏輯準位狀態切換到高阻抗狀態。

★只針對俱備高阻抗的輸出腳及雙向腳做量測。

★當使用二元搜尋法時,測試結果只會是正值。

範例:256×4靜態隨機存取記憶體

■ 規格書

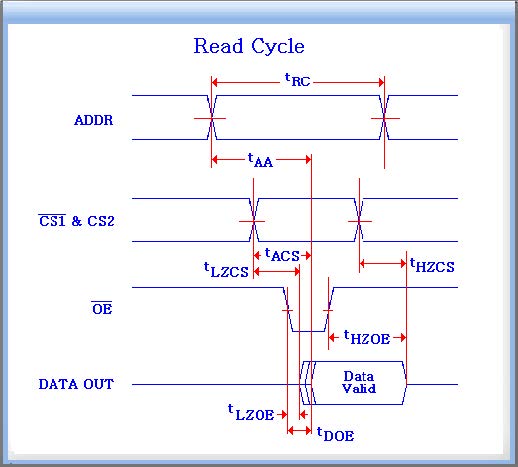

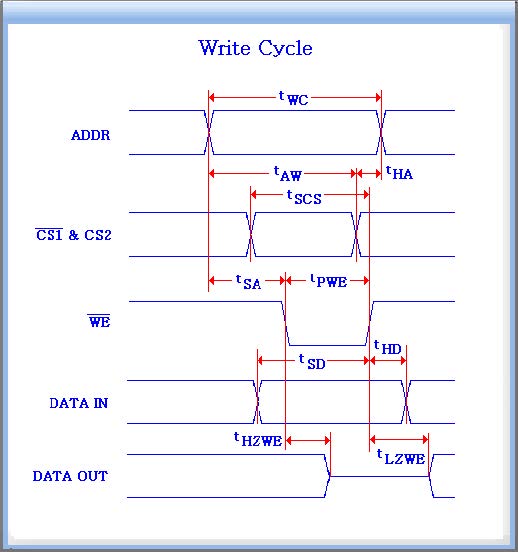

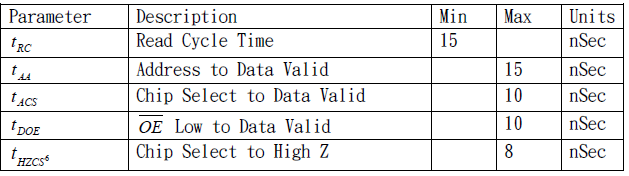

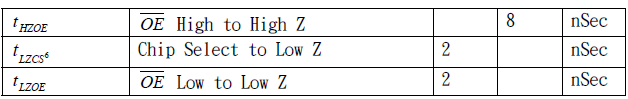

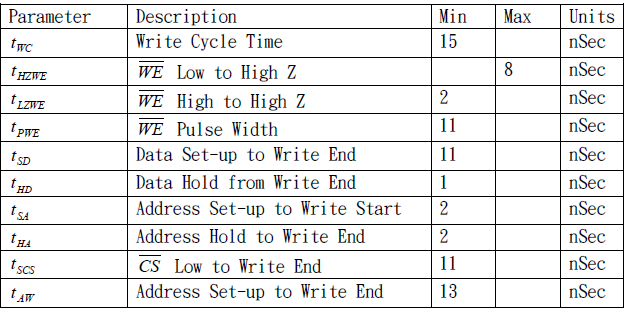

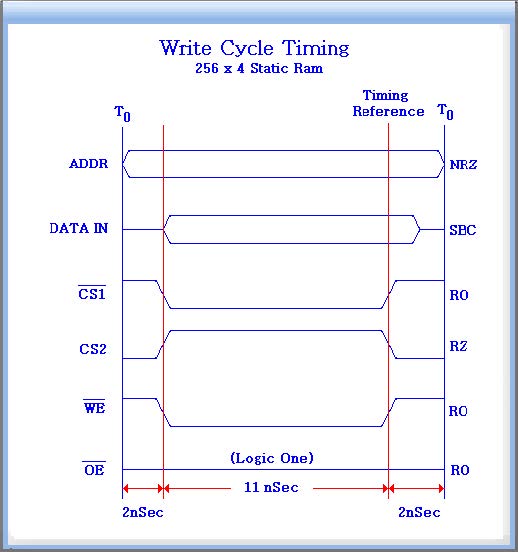

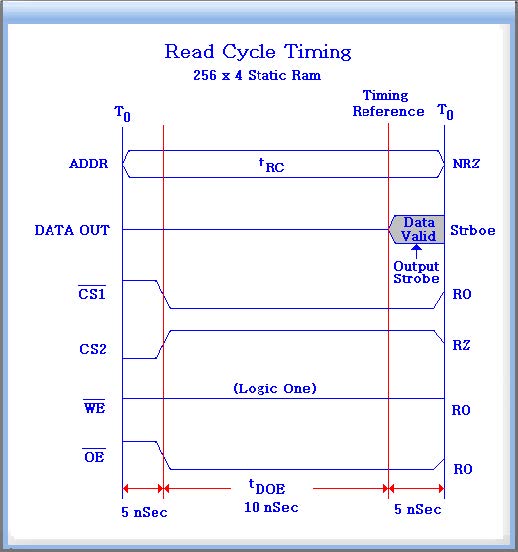

以下的表格,用來介紹256×4靜態隨機存取記憶體的交流參數規格。主要是針對讀取指令與寫入指令的時序定義做說明。圖7-8為讀取週期時序。圖7-9為寫入週期時序。

圖8

圖9

讀取指令

寫入指令

■ 建立功能參數的時序定義

如規格書中的定義,我們必需要小心地檢視時序設定。並依規格書繪出測試用的時序圖(Timing Diagram)。如果你希望達到較少的測試時間為目的的話,你需要對測試機的能力,與待測物的時序需求做匹配。使用較高檔功能的測試機時,你可能只需要使用單一的測試向量,就能夠測試所有的參數。如果使用的機台資源有限,你又必須做平行測試(Multiple Test)時,你可以對每一個功能測試,使用新的時序條件,直到所有參數都被驗證。

建立測試時序的第一步驟,就是定義測試週期的值(也稱為測試頻率)。請你儘量花一些時間,去完全瞭解待測物的時序定義。這是開發測試程式過程中,一項非常重要的工作。如果來自模擬的測試資料,已經被完成,且轉換成測試向量。請檢視模擬時的時序設定。因為,測試程式會延用這些時序設定。且模擬時的時序設定,應該與規格書中的定義相符。同時,也要與測試系統相容。

請仔細研讀前面的規格書,並完成寫入指令與讀取指令的時序設定。請依下面的步驟,完成寫入指令的時序設定工作。

1.定義測試週期的值,劃兩條垂直線,代表測試週期,並標示測試週期的值。

2.決定控制訊號的時序,並滿足前面定義的測試週期。在你的時序圖上,劃出控制訊號,並標示出控制訊號的上昇緣與下降緣的時序位置。

3.決定資料訊號的時序,並滿足前面定義的測試週期。同樣地,在你的時序圖上劃出資料訊號,並標示出資料訊號的上昇緣與下降緣的時序位置。

4.一旦訊號繪製完成,時序位置也已標明,再來就是定義每一個訊號的波形,同時請考慮控制訊號,是在哪種狀況下Active或Non-Active。

■ 寫入指令的時序

依256×4靜態隨機存取記憶體規格定義,來完成寫入指令的時序圖。

1.依WCt參數來決定測試週期。

2.再來決定可以控制寫入功能的訊號。如WE訊號的上昇緣之前,把輸入資料寫入記憶體中,所以我們應該把WE訊號看成控制訊號來看待。

3.接下來,我們應決定其它的輸入訊號。而WE訊號,其上昇緣與下降緣,在測試週期內的位置,是藉由訊號的設置時間(Setup Time),與維持時間(Hold Time)來決定。另外,定址訊號(Addressing)的時序AWt需要13nSec的設置時間,及2nSec的維持時間。這兩個參數的合為15nSec,剛好等於測試週期的時間。同時,也定義了WE訊號的上昇緣位置在13nSec。CS訊號及資料輸入訊號(Data In),它們的時序定義,也是相關於WE訊號。在寫入指令週期中,我們也可以考慮資料輸出訊號(Data Out)的時序定義,但這個考慮是可以被忽略的。因為資料輸出訊號,在寫入指令週期中,是沒有被測試到的。

劃出所有訊號的時序圖。如此,你才可以完全地瞭解,所有訊號的時訊關係。圖10,是一個寫入指令的範例。通常規格書中的時序定義,並不一定會詳細地描述它們之間的關係。使用正確的時序圖,我們可以很容易地瞭解,每一項交流測試項目,是在做些什麼事,並可依此來偵錯(Debug)。在偵錯的循環過程中,我們應該比較示波器所顯示的訊號,與時序圖之間的差異。

圖10

■ 讀取指令的時序

1.依256×4靜態隨機存取記憶體規格定義,仔細檢驗其內容,並用來完成讀取指令的時序圖。由RCt參數來決定測試週期,這個參數的時間長短,是由讀取記憶體內的資料過程中,所需的時間來決定。為了完成這樣的測試,記憶體內的資料,必需要先被讀取後,才來驗證其正確性。所以實際上測試週期所需的時間,會比規格書中的RCt參數值,來得長一點。

2. 再來就是決定控制訊號的時序定義。此控制訊號是能控制讀取功能的訊號。請注意,當輸出訊號啟動時(也就是OE下降緣的位置)。一旦輸出訊號被啟動,儲存在記憶體內的資料,就可以被讀取。因此OE就是讀取指令的控制訊號,且所有的時序設定,皆參考OE而定。

圖11

您所劃出的時序圖,可以顯示出所有訊號相關時序位置。請記得,所有的輸入訊號,必需要維持足夠的時間,以便驗證輸出訊號。圖11所示,測試時間需要額外的5nSec。這段時間是我們可以驗證資料輸出的時間。就像圖10一樣,讀取指令的時序圖,也已經被座標化。在完成一支測試程式之前,你可能需要繪製許多的訊號時序圖。至於需要多少張時序圖,則完全依電路的複雜度來決定。