第六章 – 功能參數測試

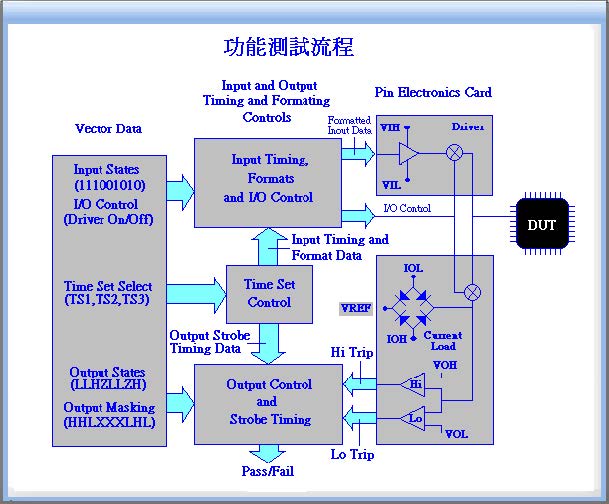

功能測試的主要目的,是驗證電路的邏輯功能是否正確地運作。為了達到測試目的,一般會利用測試向量(Test Vectors)或真值表,來偵測電路是否符合設計的要求。加入時序的測試向量,是構成功能測試的核心。同時,在考慮功能測試的同時,也必須將電路各方面的效能,作全面性的探討。例如,測試頻率、輸入腳訊號時序、輸入腳訊號格式、輸出腳訊號格式等等。這些項目,是在執行功能測試時,測試系統必需提供的資源。

功能測試,包括兩個主要的部份。測試向量檔案及測試程式主體。測試向量(Test Vectors),就是輸入腳及輸出腳的邏輯值。當功能測試在執行的過程當中,測試系統,會依測試向量提供的邏輯準位,供應到輸入腳上。並在輸出腳上取得輸出邏輯值,再依測試向量內記載的輸出期望值作比較,以判定正確(Pass)或失效(Fail)。判定條件除了期望的邏輯值之外,還包括輸出電壓及輸出時序。

功能測試的相關術語

在探討功能測試之前,有一些相關術語。需要在探討功能測試的各種量測原理與方法之前,必需先介紹給讀者認識。以便讓讀者能夠了解,功能測試是如何完成它的任務。以下逐一說明之:

■ 測試向量(Test Vectors)

測試向量(Test Vectors),也有人稱為測試圖樣(Test Patterns)。不管是測試向量,還是測試圖樣,它所代表的是電路的輸入腳與輸出腳的各種邏輯狀況。測試系統,依據測試向量的內容,運用訊號驅動電路,提供輸入訊號到待測物的輸入腳上。相同地,測試系統,利用比較電路與測試向量的內容做比較。如果與期望的值相符,則判定為正確(Pass),否則為失效(Fail)。

測試向量,通常會用0與1的數字,來代表輸入腳與輸出腳的邏輯值。目前,大部份的測試系統,不僅只用0與1來表示輸出腳或輸入腳的邏輯值。也可以用其它的英文字來表示。例如,H可以代表高電位(High Voltage)為邏輯1。L可以代表低電位(Low Voltage)為邏輯0。Z代表輸出腳處於Tri-State的狀況。X代表此輸出腳的邏輯值,是被忽略不處理的。至於是否還有其它文字的表示,端看測試機而定。

■ 測試週期(Test Cycle)

也可以用英文Test Period來稱呼。基本上,一個測試週期的時間長短,取決於Device的操作頻率。例如DDR 400的記憶體,其操作頻率為200MHz,換算成週期,則為5奈秒(nSec)。因此,要測試DDR 400的記憶體,測試週期就要定為5奈秒(nSec)。

這裡順便提醒讀者,測試機的系統頻率。一般要高於待測物的操作頻率。否則,根本無法提供應有的操作頻率給待測物來運作。同時,時序電路的解析度也要足夠,否則量測結果的可信度,會遭到質疑。

以頻率為運作基礎的電路,每一個週期可定義成一行測試向量。每一個週期的開始時間,我們都稱呼它為T0。而系統內部的時間校正及同步動作,是由系統時脈電路來維護。

■ 輸入訊號(Input Signal)

在測試領域裡,輸入腳的輸入訊號,是需要經過特殊電路的處理,才會驅動到待測物的輸入腳上。這種經過處理的訊號,一般稱為格式化的訊號(Formatted Signal)。

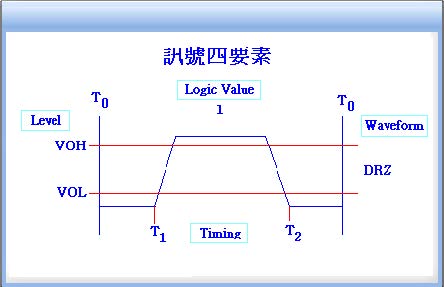

數位邏輯測試機,一般都會提供這樣的電路,來完成這個格式化的工作。訊號格式化電路,須要以下幾項訊息,才能完成它的任務。(1)測試向量。 (2)準位電壓值,VIH、VIL。(3)訊號波形(Waveform)。(4)訊號轉折點的時間設定。這四項稱為訊號四要素。

輸入訊號,也有人用英文稱呼為脈波(Pulse)。圖1為一種脈波訊號的範例。以RZ波形來表式。

圖1 訊號組成

測試程式開發人員,需要提供以上四種訊息給格式化電路,來完成這個工作。此電路,一般設計在驅動電路(Driver Channel)中。訊號經過這樣的流程處理後,才會驅動到電路的輸入腳上。

■ 輸入訊號格式(Input Signal Format)

也有人稱為訊號基本波形(Waveform)。讀者可以將訊號波形,當成訊號形狀的一種基本格式。至於有那幾種格式可使用,完全由測試機來決定。基本上,數位邏輯測試機,會提供以下幾種通用的波形。例如,RZ、NRZ、DNRZ、RO、SBC、ZD等基本波形。

讀者一定要了解各波形的定義。因為,要產生一個脈波訊號之前,您一定要先確定,你要用哪一種波形來產生。選擇波形的技巧,除了需要一些經驗外,基本上,要從待測物輸入腳的定義,及測試的目的來決定。這樣講讀者一定會很納悶。以下儘可能提供實例來說明,讀者就能一通百通。另外有一個觀念,讀者一定要認知。對一個Device而言,我們會對它做許多項的測試。每一根腳的波形選擇,不是重頭到尾所有的測試項目,都採用同一個波形。而是根據測試項目的目的,來決定波形。

說明第一個RZ波形之前,先來探討「訊號轉折點的時間設定」。之前的章節曾經介紹過,頻率、週期、及測試週期這些觀念。讀者應該已經了解並融會貫通。現在我們要探討的是,在一個測試週期內,提供一個脈波訊號到輸入腳上。而這個波形的長像,希望以何種形式來顯示呢?

首先,需要將一個測試週期,區分為幾個時間間隔。之前提到每一個週期的開始時間命名為T0。T0就是波形的第一個時間轉折點。皆下來讀者應該會提問,會有幾個時間轉折點呢? 答案是依測試機的硬體設計來決定。一般會有T0,T1,T2三個時間轉折點。有的測試機甚至提供到T5。這些時間轉折點的命名方式,由各家廠商來決定。有的會用保留字的方式,有的則用參數位置的方式來表達。

訊號的設置(Set)動作。當訊號在設定的時間點上,依邏輯值作設定的動作,英文稱之為Set。相反地,訊號也有重置(Reset)動作,它的解釋是,當訊號在重置的時間點上,作回覆的動作,英文稱為Reset。

以下的波形,就是要告訴我們,Set動作在何時做。Reset動作在什麼條件來執行。以下逐一說明這些波形的定義。

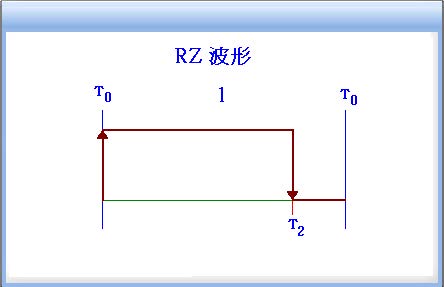

▲ RZ波形

RZ是Return to Zero的簡稱。中文翻譯為「回到零」。用以上幾個英文單字來解釋RZ波形,初學者很難完全體會它真正的定義。它比較完整的定義是,Set動作之前,維持前一週期的邏輯值。Set動作依其邏輯值作設定。如果是1就設為1,如果是0就設為0。並維持邏輯狀態到Reset動作發生之前。而Reset動作,一定將邏輯值回到0的狀態,並維持到下一個週期的開始。

所以RZ波形需要用到一個時間轉折點T2。請注意T0是固定不變的週期原點。T2是可變動且可隨意調整的。一般Set會設在T0,而Reset會設在T2。

圖2為RZ 波形的一個範例。Set 設在T0,Reset設在T2。T0=0nSec,T2=80nSec,Test Cycle=100nSec。

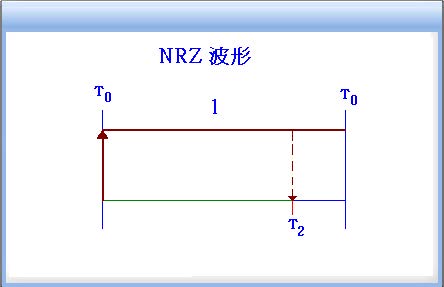

▲ NRZ波形

NRZ是Non Return to Zero的簡稱。顧名思義它在Reset動作是不強迫回到0的狀態。它完整的定義是,Set動作之前,維持之前的邏輯值。Set動作依其邏輯值作設定。如果是1就設為1,如果是0就設為0。Reset動作時維持原有邏輯值,持續到下一個週期前。

所以NRZ波形需要用到一個時間轉折點T2。圖3為NRZ 波形的範例。Set 設在T0,Reset設在T2。T0=0nSec,T2=80nSec,Test Cycle=100nSec。

圖3

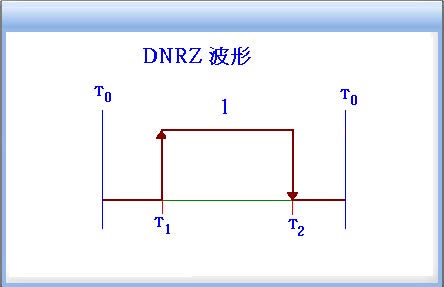

▲ DNRZ波形

DNRZ是Delayed Non Return to Zero的簡稱,其定義與NRZ相同。但在Set動作之前,一定要有一段延遲時間。NRZ不須要延遲時間。所以DNRZ的Set動作,可設在T1。

DNRZ波形需要用到兩個時間轉折點T1,T2。圖4為DNRZ 波形的範例。Set 設在T1,Reset設在T2。T1=20nSec,T2=80nSec,Test Cycle=100nSec。

圖4

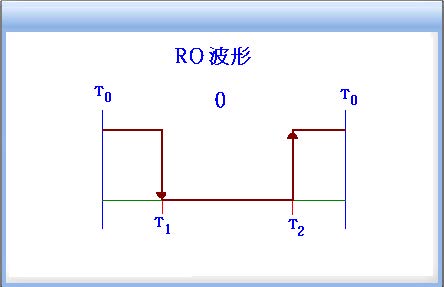

▲ RO波形

RO是Return to One的簡稱。中文翻譯為「回到1」。它的完整定義是,Set動作之前,維持前一週期的邏輯值。Set動作依其邏輯值作設定。如果是1就設為1,如果是0就設為0。並維持邏輯狀態到Reset動作發生之前。而Reset動作,一定將邏輯值回到1的狀態,並維持到下一個週期的開始。

所以RO波形,需要用到兩個時間轉折點T1,T2。讀者可以將RO與RZ簡單的比較一下,更能加深印象。

圖5為RO 波形的一個範例。Set 設在T1,Reset設在T2。T1=20nSec,T2=80nSec,Test Cycle=100nSec。

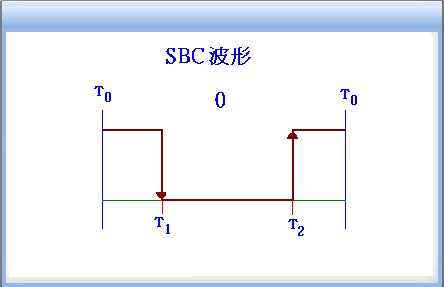

▲ SBC波形

Surround By Compliment的簡稱。中文翻譯為邏輯值的前後必需以補數的方式來表示。完整的定義為,Set動作之前以補數表示。Reset動作之後,也以補數來表示。因為,數位訊號不是0就是1。所以0的補數為1,而1的補數為0。

所以SBC波形,至少需要用到兩個時間轉折點T1,T2。另一種XOR波形與SBC很相似。但它用三的時間轉折點T1、T2、T3。

圖6為SBC 波形的一個範例。Set 設在T1,Reset設在T2。T1=20nSec,T2=80nSec,Test Cycle=100nSec。

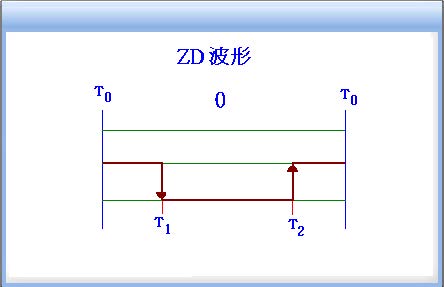

▲ ZD波形

Z代表Impedance的意思。中文翻譯為「高阻抗」。D為Drive之意。這個波形,當驅動電路關閉時,設為高阻抗(High Impedance State)狀態。當驅動電路打開時,依邏輯值來表示。

所以ZD波形至少需要用到兩個時間轉折點T1,T2。圖7為ZD 波形的一個範例。Set 設在T1,Reset設在T2。T1=20nSec,T2=80nSec,Test Cycle=100nSec。

圖7

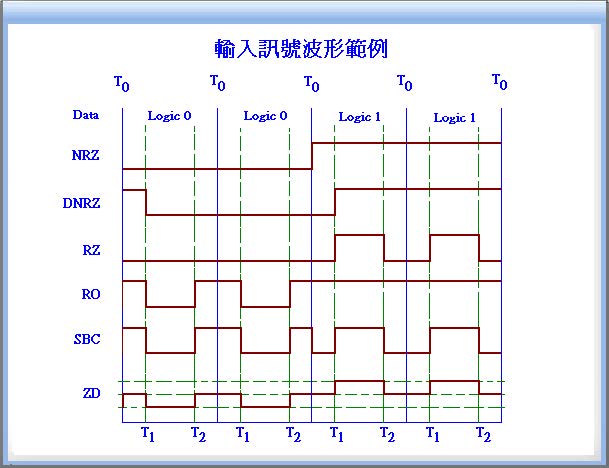

■ 輸入訊號的範例

圖8

一旦測試週期的時間確定後,時間轉折點T1,T2就可以定義。對輸入腳而言,有些腳是控制用,而有些腳是傳輸資料用。因此,輸入訊號可分為控制訊號,及資料訊號。接下來,便可以決定訊號的上下邊緣,也就是設定Set的時間點,就是設定T1就對了。接著,設定訊號的維持時間(Hold Time),就是T2的時間點。再來,就是決定訊號的波形。一般時脈訊號(Clock)會用RZ波形,或RO波形。

CS(Chip Selected)採用RZ波形的也不少。/CS,/OE則採用RO波形較多。資料腳採用SBC波形比較常見。主要是資料腳有設置時間(Setup Time)及維持時間(Hold Time)上的問題。其它輸入腳,則採用NRZ或DNRZ的波形即可。

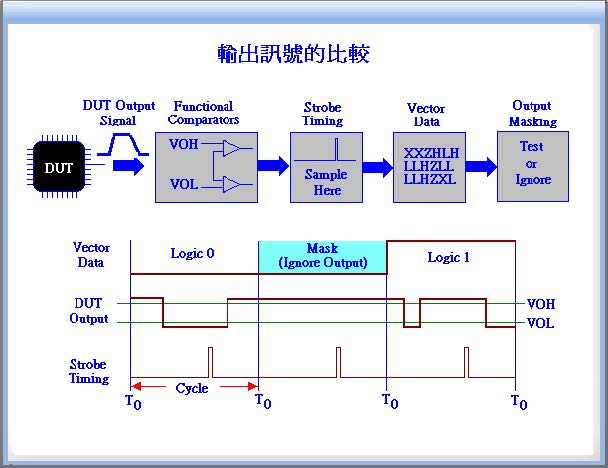

■ 輸出取樣(Output Sampling)

功能參數測試時,為了瞭解其輸出腳的輸出訊號,是否符合設計規範,當然必需要經過一個量測過程。這個量測的時間不會很長。一般會是在測試週期內一個短暫的時間點上。這樣的動作,我們稱為輸出取樣(Output Sampling)。

■ 輸出遮罩(Output Mask)

這是一種可以將測試通道中的比較電路,做開與關的動作。也就是說,我們可以設定某一個測試週期,將比較電路關閉。這樣的設定動作,稱為輸出遮罩(Output Mask)。

■ 輸出訊號的量測

在數位邏輯電路的功能參數測試中,需要以下的訊息,測試機的比較電路,才有辦法判斷出正確(Pass)或者是失效(Fail)。(1)輸出腳的期望輸出值,這個值會被事先存放於測試向量中。(2)輸出取樣時間。(3)期望輸出準位VOH、VOL。(4)輸出腳的電流負載。

在做功能測試的過程當中,首先要知道輸出取樣時間。在這個時間點上,做輸出取樣的動作,以便取得輸出電壓值。皆下來,依據VOH與VOL的值,判斷輸出訊號的電壓準位,是高準位還是低準位。再與測試向量中的值做比較,最後會得到正確(Pass)與失效(Fail)的結果。

■ 功能測試的流程範例

圖9

■ 正常情況下的輸出準位

輸出電壓≧VOH時為邏輯1。輸出電壓≦VOL時為邏輯0。

■ 高阻抗輸出準位

高阻抗輸出準位,一般定義為大於VOL且小於VOH的輸出電壓值。

我們稱呼為高阻抗輸出準位(High Impedance Output Levels)。如果想要知道,輸出腳是否處於高阻抗準位,可以利用功能參數測試的方式,來得到想要的結果。這個時候,比較電路必須反向來判斷,並將正確(Pass)與失效(Fail)的結果送出。

這裡要特別注意,當輸出腳為高阻抗輸狀態時,輸出腳會失去供應電壓或電流的能力。您可以將高阻抗輸出,用以下的狀態看待。當高阻抗輸出時,輸出腳停留在之前的合法邏輯值。除非某些外在因素的影響而改變。例如,外在負載會將輸出電壓,拉到參考電壓的電位。

■ 輸出電流負載(Output Current Loading)

功能測試時,待測物會被供應一個電流負載到輸出腳上。這樣的目的,是要模擬待測物,在實際電路上的真正狀況。這個可程式化電流負載電路,也可稱為動態負載。可程式化的意思是,負載的大小可以由程式來決定。而這個負載電路,一般都會設計在PE 卡上面。如果測試系統,未提供電流負載電路時,我們必需自行在測試電路上,外加電阻的方式,來達到負載的目的。負載電流的大小,以IOL及IOH來決定。這樣的方式,比使用PMU來量測,其速度會比較快。

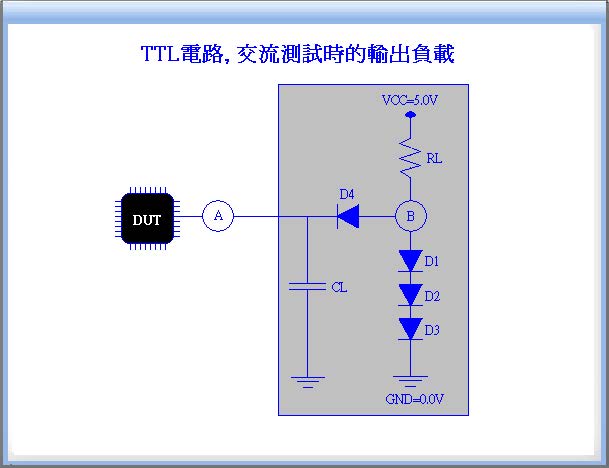

■ 交流測試時的輸出負載

當執行交流測試時,一般測試規格書,都會標明輸出腳的電流負載。這些負載,可能是用電阻或電容或二極體所形成的電路。它主要是模擬實際應用時的狀況。這種型態的負載,通常在測試TTL電路時用到。

圖6-10是一個交流輸出負載的一個範例,請注意觀查B點的電壓及電流變化。當A點還接在待測物的接腳上時,這個負載電路在B點的電壓為2.1V。因為三個二極體串接後接地,每一個二極體電位差為0.7V,故B點的端電壓為2.1V。因此,跨接於電阻兩端的電位差為5.0V-2.1V=2.9V。

流經電阻的電流為2.9V/2000Ω=1.45mA。

當負載電路接上待測物輸出腳後,輸出腳被驅動為邏輯0(如果VOL=0.4V時)則A點端電壓為0.4V。這時B點端電壓為0.4V+0.7V=1.1V。流經電阻的電流為(5.0V-1.1V)/2000Ω=1.95mA。因此,當輸出腳為邏輯0時,其電流負載為1.95mA。

當負載電路接上待測物輸出腳後,輸出腳被驅動為邏輯1(如果VOH=2.4V時)則A點端電壓為2.4V。這時候D4的二極體形成逆向偏壓,因為B點電壓為2.1V。因而無法形成電流負載。這個範例是說明,當輸出腳被驅動為邏輯0時,會有一個電流負載1.95mA。

當輸出腳被驅動為邏輯1時,這個電流負載就會被移除掉。

圖10

■ 輸出訊號的時序定義

輸出腳的訊號輸出,通常由系統時脈,或者是控制訊號的邊緣來控制。想要完全了解這種的狀況的真正原因,您必需要瞭解待測物的訊號時序圖。你要了解,是由系統時脈的邊緣來控制,還是由控制訊號的邊緣來控制。並且要了解輸出腳到達邏輯值的輸出準位,需要多久的延遲時間。知道這個延遲時間之後,我們就可以定義,輸出取樣時間。輸出取樣,一般以英文Output Strobe來稱呼。取樣時間,可以是一個切點的時間,或者是一小段時間的連續取樣。這完全依測試硬體是否提供此一功能而定。輸出電位大於VOH時,則為邏輯1。輸出電位小於VOL時,則為邏輯0。將量測結果與測試向量的期望值做比較。如此,即可判斷出正確(Pass)與失效(Fail)。

圖11

■ 一般功能測試的執行步驟

以下是一般功能測試的執行步驟:

1.決定VDD電源電壓值。

2.決定輸入腳與輸出腳的邏輯準位電壓值(VIL/VIH/VOL/VOH)。

3.決定輸出電流負載(IOL/IOH/VREF)。

4.決定測試週期。

5.決定所有輸入腳的訊號波形。

6.決定輸出取樣時間。

7.決定測試向量的啟始位置與結束位置。

8.執行功能測試。

■ 功能測試時的幾項考慮因素

一般在做功能測試時,有兩種測試方法可以考濾。第一種,將所有輸入腳與輸出腳的時序參數,定義的很嚴格。也就是假設在最壞的情況下,去執行功能測試。同時,測試向量也以最嚴格的角度來思考。這種測試方法,它可以很快且保證能夠符合測試規範。但有一項缺點是,當失效發生時,無法得知那一項因素所引起的失效。

另外一種方式是,逐項的來測試。例如,先將規格書設定的VIL/VIH值固定,而將其它參數放鬆來測試。如果因此而失效,我們就可以很容易地判斷出,是VIL或者是VIH的所引起的失效。運用此方法,直到所有參數都被驗證過。這種方法,可以得到很多的訊息,以便了解失效發生的原因,但會增加相當多的測試時間。

功能測試時,如果給與的測試條件,是比較能夠讓待測物通過測試的話,這樣的測試,稱為寬鬆參數的測試方法。舉例來說,VIL的規格定為0.8V,如果測試條件改為0.4V時,我們稱為放寬測試參數。因此,對於輸入腳而言,VIL值調得越低或者VIH調得越高時,測試參數就越寬鬆。而對輸出腳而言,將VOH與VOL設為相同值時,測試參數就比較寬鬆。

例如 VOH = VOL = 1.2V。這個時候,只要低於1.2V時就可判定為0。相反地,大於1.2V就判定為1。這裡特別注意,對於Z-State是無法放鬆參數條件的。對於時序參數的放鬆,我們可以考慮將測試頻率放慢。或者增長設置時間(Setup Time)或維持時間(Hold Time)。或者延長遞延時間。

規格表通常會定義VDD的操作電壓範圍,例如:VDD=5.0±10%,它要表達的是電壓最小為4.5V,最大為5.5V。最大電壓以VDDmax表式,而最小電壓以VDDmin表式。一般功能測試,要求含概整個範圍。因此,需要測試兩次。一次以VDDmax作測試,另一次以VDDmin測試。

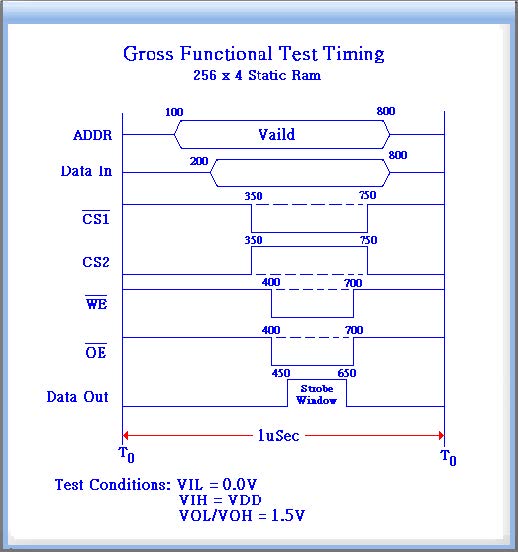

第二節 寬鬆條件的功能測試

所謂寬鬆條件的功能測試(Gross Functional Test),這個術語就是在執行功能測試時,所給的條件是比較寬鬆的。例如,頻率、時序、電位、電流負載等所有的條件,都是比較寬鬆的。英文有時候稱為「Basic Function Test」或「Wiggle Test」。

■ 為何要測試寬鬆條件的功能測試呢?

寬鬆條件的功能測試,其主要的目的,是要看看待測物在此條件下,是否還能正常地工作,或稱為「活著(Alive)」。而這些條件,應該要能夠讓待測物,很輕易地通過測試,並且確認測試向量是正確無誤。當程式開發之初,寬鬆條件的功能測試,通常被用來驗證測試向量是否正確。另外,以測試流程的觀點來看,寬鬆條件的功能測試,會被放在測試程式之前。如此,可以確定後續的所有功能測試項目,其使用的都是正確的測試向量。

■ 寬鬆條件的功能測試方法

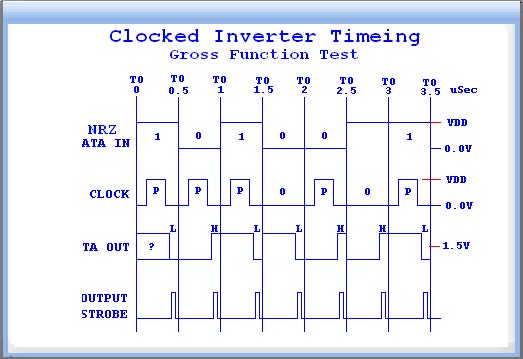

圖12是2564靜態記憶體的寬鬆條件功能測試時序圖。而其交流參數規格,則在第七章中會加以說明。其中的操作頻率為66MHz。由圖12得知,輸入準位、輸出準位、時序設定等,都會是比較寬鬆的條件,且操作頻率由66MHz降到1MHz。同時,所有的設置時間(Setup Time)、維持時間(Hold Time)、遞延時間(Propagation Delay Time),也都設定在比較寬鬆的條件之下。但請特別注意,當你放寬條件之後,你必需維持所有時序之間的相對關係。這個範例也說明了VIL、VIH、VOL、VOH等電壓準位的寬鬆條件。

一旦待測物,可以通過寬鬆條件的功能測試。接下來,會有較嚴格的測試項目,來確保待測物符合所有的規格。但是,當比較嚴格的測試項目失效的同時,我們為了找到增加測試產量的方法,寬鬆條件的功能測試,是可以有條件地扮演此一角色。當量產測試時,寬鬆條件的功能測試,通常會提供有價值的良率訊息。

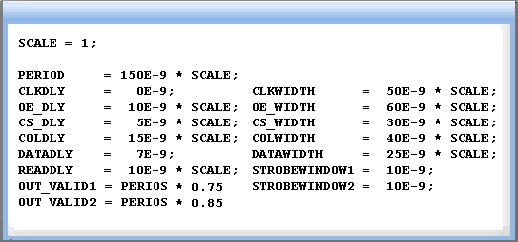

■ 時序設定方程式

在開發功能測試時序圖時,時序值的設定方法,要能夠很方便地修改。這點 6-18 白安鵬彙編 第六章 功能參數測試 在測試程式的開發與偵錯的過程當中,是相當重要的。我們可以使用程式變數,並以方程式的方式,來加以設定。如此一來,我們就可以很容易地更改變數的值,並完成整體的時序設定。以下這個範例,如圖13所示。說明測試程式中的時序設定,只要修改Scale這個變數,就可以讓時序的設定,變得嚴謹(Tightened)一點,或是變得寬鬆(Relaxed)一點。

■ 執行功能測試

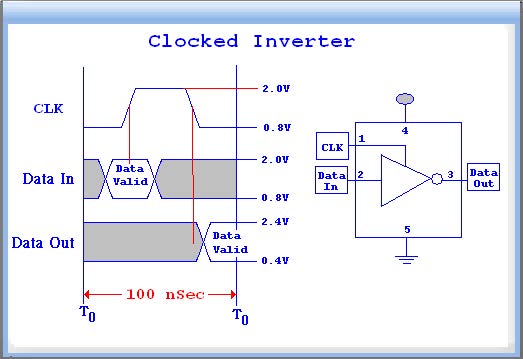

以下討論的目的,是要對待測物的規格、測試系統的硬體、與測試程式之間 的相關性,做一點點複習的工作。以便對待測物做基本的功能測試。我們會用一個俱備時脈訊號的反向器(Clocked Inverter)來做範例。此反向器有兩個輸入腳,一為時脈輸入腳(Clock Pin),另一為資料輸入腳(Data In)。同時還有一根資料輸出腳(Data Out)。此反向器的功能說明如下:

1. 時脈訊號是屬於控制訊號,它可以控制資料輸入訊號,經過反向器後,出現在資料輸出腳上。

2. 當時脈訊號,由低電位變成高電位(上昇緣)時,輸入腳上的訊號,會被讀入反向器的電路中。

3. 當時脈訊號,由高電位變成低電位(下降緣)時,反向器內部訊號,會被輸出到輸出腳上。

4. 只有時脈訊號存在時,訊號才會被傳送。

5. 輸出腳的邏輯準位,是輸入腳的邏輯補數值(也就是反向值)。

圖13

■ 反向器的規格 以下的訊息,定義了反向器的電壓準位與時序。通常規格表的內容,代表的是最差的條件,且待測物必須要符合此規格。這也是測試人員,用來開發測試程式的依據。如圖14所示。

VDD = 5.0V

VIH = 2.0V, VIL = 0.8V

VOH = 2.4V, VOL = 0.4V

Operating Frequency = 10MHz, Clock Duty Cycle of 50%

Data In Setup Time = 15nSec

Data In Hold Time = 5nSec

Output Propagation Delay Time = 8nSec

其它相關訊息,請參考第七章的說明。

圖14

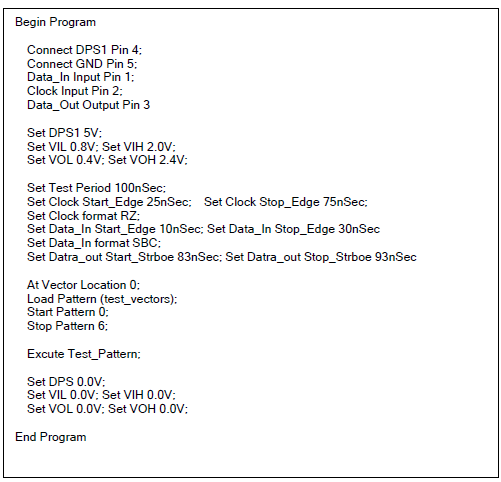

■ 設定測試機

為了要保證待測物符合規格,測試硬體必需要能夠俱備一種設定方法,來驗證每一種測試參數。首先,我們針對DPS(Device Power Supply)做設定。DPS主要是要提供VDD電壓給待測物用。此例VDD會設定為5.0V的電壓,就如規格中所描述的。而待測物的接地點,會連接到測試機的接地面(Ground Plane)上。

而測試機的RVS(Reference Voltage Supply),會提供電壓準位給PE卡上的驅動電路來使用。VIL的值會被設定為0.8V,VIH的值會被設定為2.0V。當邏輯值為0時,VIL的電位,會被驅動到輸入腳上。相同地,當邏輯值為1時,VIH的電位,會被驅動到輸入腳上。同時,RVS也提供電壓準位,給PE卡上的比較電路 6-21 第六章 功能參數測試 白安鵬彙編 來使用。這個比較電路,會去感應輸出腳上的電位,並與VOL/VOH的電壓值做比較。此例,我們會設VOL=0.4V,VOH=2.4V。當測試向量中的輸出腳,其邏輯值為0時,PE卡上的比較電路,會將感應到的電壓值與VIL的參考電位做比較。如果感應到的電壓值,大於VIL的參考電位,這時會送出一個失效的訊息。相同地,當測試向量中的輸出腳,其邏輯值為1時,PE卡上的比較電路,會將感應到的電壓值與VIH的參考電位做比較。如果感應到的電壓值,小於VIH的參考電位,這時也會送出一個失效的訊息。

測試機的相關時序硬體資源,對於輸入腳而言,可以用來定義測試週期、訊號格式、時序位置(Edge Placement)。同時,也被用來定義,何時對輸出腳做取樣(Output Strobe)。然而,開發時序的第一步驟,是決定測試週期的長短。如果規格表定義的測試頻率為10MHz時,則測試週期的時間為100nSec。公式為頻率週期1=。規格表也指出了,時脈訊號的Duty Cycle為50%。也就是一個時脈訊號,在一個測試週期中,50nSec為高電位,50sSec為低電位。以此範例來說,時脈訊號前25nSec為低電位,接下來50nSec為高電位,再來的25nSec為低電位。為了能正確地產生時脈訊號,我們會使用RZ波形來產生此一訊號。

而Data In這個輸入腳的時序設定,是與時脈訊號相關連的。Data In的設置時間,是時脈訊號上昇緣之前,要有15nSec。而維持時間是上昇緣之後,要有5nSec。因此,Data In的訊號脈波寬度,要有20nSec。為了驗證設置時間及維持時間,Data In的訊號波形,我們會採用SBC波形。後面的章節中,會再討論設置時間與維持時間的參數量測。

開發時序的最後一個步驟,是對輸出腳做取樣時間的設定。規格中指出遞延時間,為時脈訊號下降緣之後的8nSec。因此,此範例我們可以將輸出訊號的取樣時間設定為83nSec。如果輸出腳是在正確的邏輯狀態(如真值表所預期的),取樣後會與VOL及VOH做比較。如果比較後是正確的結果,就會送出一個正確的訊號出來。後面的章節,還會對遞延時間做進一步地說明。

我們還需要一個測試向量檔,來驗證待測物的功能測試參數。這個測試向量檔的內容,我們可以用手寫的方式來完成。因為,此待測物的電路功能,相當地簡單。此測試向量檔,會被儲存在測試向量記憶體內。當每次執行該項功能測試時,此測試向量就會被執行一次。

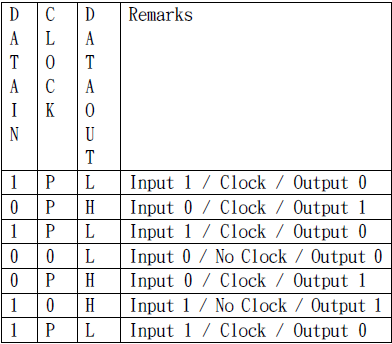

■ 測試向量 之前提過,我們需要一個測試向量檔。它有時稱為真值表。執行功能測試時,我們需要用到這個檔案。一般而言,測試向量檔內,會由一些數字與英文字母,所組合而成。這些數字與英文字母,所代的是輸入腳與輸出腳的邏輯狀態。而此範例,是由7行測試向量所組成。每一行測試向量,代表一個測試週期。然而,測試訊號(Test Vector Data),是由時序、波形、及電壓準位所組合而成。我們可以由圖15,得知完整的測試過程。反向器的測試向量,如表1所示。

測試向量的向量字母如下說明:

1:代表輸入腳為邏輯1的狀態。

0:代表輸入腳為邏輯0的狀態。

H:代表輸出腳為邏輯1的狀態。

L:代表輸出腳為邏輯0的狀態。

P:代表提供輸入腳,一個脈波訊號。

表1

■ 反向器的測試條件

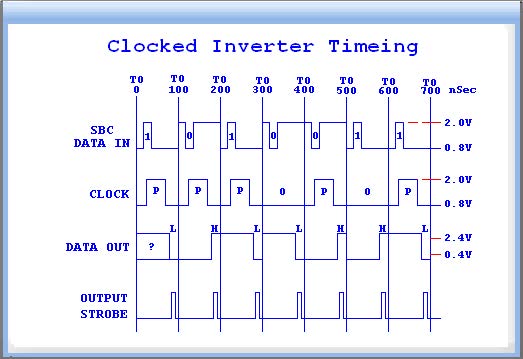

圖15顯示出功能測試時的測試過程。圖中,顯示出7個測試週期,且每一個訊號,都由時序、波形、準位所組合而成。圖中所顯示的訊息,皆反應出規格表中,所定義的參數內容。功能測試頻率設定100nSec。

時脈訊號的Duty Cycle 6-23 第六章 功能參數測試 白安鵬彙編 為50%,且以RZ波形來表示。而Data In以SBC波形來表示。同時,輸入腳與輸出腳的準位,皆以規格表的內容加以設定。

圖15

■ 反向器寬鬆條件的功能測試

寬鬆條件的功能測試,通常是很有用的。其目的是在寬鬆條件下(此條件與規格表中的參數定義無關),待測物是否能夠正常地工作。有時候,依規格表定義的條件測試時,其測試結果可能會失效。此失效的原因,可能是因為一個或多個測試參數所引起。這些參數可能是輸入準位、或是輸出準位、或是時序的關係所引起。它也可能是因為矽製程所引起的失效。

圖16所顯示的訊號,代表執行寬鬆條件的功能測試,其相關時序與電位條件。其中,輸入腳與輸出腳的電壓準位,已經被修改過(放寬)。它從100nSec變成500nSec。而Data In的訊號,只有在每個測試週期的開始時才改變。因此,我們改用NRZ波形(NRZ波形沒有設置時間與維持時間的問題)。另外遞延時間,也要因此而延長。

如果待測物依圖15的條件測試,且測試結果為失效時,你可以用圖6-16 6-24 白安鵬彙編 第六章 功能參數測試 的條件,再重測一下。如果以寬鬆條件測試,且通過測試的話,之前測試失效的原因,就不是因為矽製程所引起的失效。寬鬆條件的功能測試,在開發測試向量的過程當中,常被拿來使用。其主要的目的,是要確認開發出來的測試向量,是否正常。

圖16

當某一個測試參數的值被放寬時,對待測物而言,更容易通過功能參數的測試。舉例來說,如果規格書的VIL=0.8V,當需要放寬條件時,我們可以將VIL設為0.0V。將VIL的電壓值降低,表示對VIL的條件做放寬的動作。也就是對待測物而言,更能夠判斷成邏輯0。另外,對VIH而言,拉高電位,就表示對VIH的條件做放寬的動作。然而,對輸出腳的放寬,其做法是將VOL與VOH的值皆設為1.5V。比較電路會將感應到的電壓值,與1.5V做比較。如果小於1.5V時,就判斷為邏輯0,如果大於1.5V時,就判斷為邏輯1。對於時序的放寬做法,有降低測試頻率、增加設置時間與維持時間、還有延長輸出遞延時間。

■ 反向器的測試程式

以下的測試程式,是用虛擬碼的方式來撰寫。

VIL/VIH 參數測試—測試向量法

雖然,每一個電路都是唯一的設計。同時,還需要一組唯一的功能測試向量。但是,有些測試參數,確可以藉由功能測試的方法,來加以驗證。接下來,就是要探討有哪些測試參數,可以用測試向量的方法,來達到驗證的目的。讀者還記得開路及短路這個測試項目嗎? 在本書的第三章第三節中,就有加以說明。如果讀者,當初未能完全瞭解其內容。筆者建議您,應先回到該節,再仔細研讀一次。該節中,就是介紹開路及短路測試。其使用的方法,也就是測試向量法。以下的章節(包括此節),都將以測試向量法,來說明直流參數的驗證。在此順便一提,筆者的經驗是,量測電流型式的直流參數,一般會用PMU的方式來量測。而量測電壓型式的直流參數,為了速度上的考量,皆以測試向量法來測試。

■ VIL/VIH測試項目

VIL的值,是輸入腳代表邏輯0時,最差狀況下的電壓值。相同地,VIH的值,是輸入腳代表邏輯1時,最差狀況下的電壓值。以下的表格,是說明2564靜態記憶體的VIL/VIH規格參數。

| Parameter | Description | Test Conditions | Min | Max | Unit |

| VIH | Input High Voltage | 2.2 | V | ||

| VIL | Input Low Voltage | 0.8 | V |

■ 為何要測試VIL/VIH測試項目呢?

這個測試項目的目的,是要保證輸入腳在此狀況下,仍然能判斷出正確的邏輯值。

■ VIL/VIH測試—測試向量法

雖然規格表中,VIL/VIH是歸類於直流參數的項目底下。但它們在驗證時,經常使用到測試向量的量測方法,來加以驗證。這種做法,是依規格表中的VIL及VIH的值做設定。設定完成之後,再執行測試向量來達到目的。如果通過測試,就表示待測物符合VIL/VIH的規格。相反地,待測物就不符合VIL/VIH的規格。

以TTL邏輯電路而言,VIL的邏輯準位一般為0.8V,而VIH為2.0V。對CMOS邏輯電路而言,VIL為VDD電位的某一個百分比。例如,VIL=0.3VDD, VIH=0.7VDD。請注意,VIL/VIH參數測試時,一般需要重複兩次的測試,一次是在VDDmin的條件下,另一次是在VDDmax的條件下測試。

■ 問題排除

當你在測試此項目且遇到問題時,請先開啟測試記錄器,並觀察測試記錄。如果你有一顆良品樣本(Golden Sample)時,請對它做一次測試,並觀察測試記錄。當測試結果為失效(Fail)時,一般會顯示出一根或多根輸出腳的訊號,是錯誤的邏輯狀態(因為,我們是使用測試向量的方法,所以會在輸出腳上做判斷)。當待測物是一個很複雜的電路時,要知道哪一根或哪一些輸入腳的VIL/VIH所引起的失效,是很困難的。除非你一根一根,單獨地測試。

讓我們從放寬VIL/VIH的電壓準位開始。放寬VIL的方法,是降低VIL的電壓準位。零電位是VIL最寬鬆的值。另外,放寬VIH的方法,是拉高VIH的電壓準位。VDD電位是VIH最寬鬆的值。放寬條件後,再重新執行該項測試。如果以最寬鬆的條件測試時,我們應該可以預期,它會通過該項測試才對。因為,測試VIL/VIH時,我們已經假設,它已通過寬鬆條件的功能測試項目(Gross Functional Test)。

接下來,將VIH的值設回原規格表的值,並重新測試。如果通過該項測試,則代表VIH符合規格表中的規定。且失效的原因,是因為VIL所引起。但,如果測試結果是失效的話,先放寬所有輸入腳VIH的值,再單獨一根一根地做放寬VIH的設定。這個方法,是一次驗證一根輸入腳。相同地,你也可以用以上的方法來驗證VIL參數。

在排除問題的過程當中,輸出電流負載,或是高頻條件下的測試,兩者有可能引起電路內部的雜訊,進而影響到VIL/VIH的測試。因此,你可能需要排除所有的輸出負載電流,或是降低測試頻率,來達到消除雜訊的目的。

請小心地閱讀產品規格書,或許規格書會指出,無靜態雜訊環境(Static Noise Free Environment)下的VIL/VIH的電壓準位。這也就暗示了,VIL/VIH電壓準位,在量產測試時,需要稍微地放寬一些。

VOL/VOH 直流參數測試—測試向量法

VOL代表輸出腳為邏輯0時的最大電壓值。IOL代表輸出腳為邏輯0時的最大電流值。VOH代表輸出腳為邏輯1時的最小電壓值。IOH代表輸出腳為邏輯1時的最大電流值。以下的表格是2564靜態記憶體的VOL/VOH的參數規格。

| Parameter | Description | Test Conditions | Min | Max | Unit |

| VOH | Output HIGH Voltage | VDD=4.75V, IOH=-5.2mA | 2.4 | | V |

| VOL | Output LOW Voltage | VDD=4.75V, IOL=8.0mA | | 0.4 | V |

■ 為何要測試VOL/VOH 直流參數呢?

其主要的目的,是要驗證輸出腳在某負載情況下,分別驗證在高電位與低電位下的輸出阻抗。也就是輸出腳在特定電流負載(IOL/IOH)條件下,仍然能維持正確的VOL/VOH的電壓值。這樣的目的,其實有兩種方法可以達到目的,一種就是使用PMU的方法來量測。另一種,也就是這個章節中介紹的測試向量法。利用測試向量法,有一個很明顯的好處就是速度快。

■ VOL/VOH 直流參數量測—測試向量法

量測的方法中,有所謂的靜態法及動態法。靜態法,就是使用PMU的方法來量測,而動態法就是利用測試向量法來量測。如果要用測試向量法來量測時,測試機的比較電路,其參考電壓準位,要依規格表中的VOL/VOH的值來設定。同時,負載電流也必需要設定上去(你可以用動態負載電路或外部電阻負載來實現它),完成以上設定後,你再去執行測試向量。

測試的過程當中,輸出腳必須要能夠吸入或供應正確的電流負載。同時,比較電路必需要確認輸出腳仍維持在正確的電壓準位,不管是VOL或是VOH。如果輸出腳是比較脆弱的(Week),並且沒有辦法吸入或供應正確的電流負載。這時,比較電路偵測到的電壓值,會超過VOL/VOH的限制範圍。因此測試結果會失效。

請注意,在執行測試向量時,如果有加掛輸出負載,會使得待測物的內部,產生較高的電流。如果輸出腳數量比較多,或者待測物有較高的電流輸出到緩衝器時,我們沒有必要同時在所有的輸出腳上,加掛輸出負載。

待測物內部有高電流時,有可能會產生雜訊。這個雜訊,可能會發生在輸出腳上,使得比較電路在做VOL/VOH電位比較時,形成失效的結果。如果有這個問題發生時,我們只要對少數的輸出腳,加掛些許的電流負載,並重新測試,直到該項目通過測試。在某些條件下,有可能需要減少測試頻率,並將取樣時間往後移動,以便通過測試。

請確定規格內的參數值,是否正確地被使用在測試程式當中。VOL通常被設定為0.4V,而VOH通常被設定為2.0V。而輸出電壓準位,通常會與電壓源有關。我們通常用以下的公式來設定。VOL = ( GND + 0.1V )或者VOL = ( VSS + 0.1V ),而VOH = ( VDD – 0.1V )。

■ 問題排除

在處理問題之前,請先啟動測試記錄器,並觀察測試結果。如果你有良品樣本(Golden Sample),請先對它測試一遍,並觀察測試結果。如果測試結果是失效的,我們會看到一根或更多根的輸出腳,其輸出的邏輯狀態是不正確的。請觀察每一根失效的輸出腳,看看是否都失效在邏輯1的狀態,還是失效在邏輯0的狀態。如果都有的話,代表VOL與VOH電壓準位都會失效。如果只有其中一種的話,就代表VOL或者是VOH電壓準位會失效。請放寬 VOL/VOH電壓準位,直到通過該項測試。同時,你也可以放寬IOL/IOH的負載電流值,並企圖通過該項測試。

請注意,輸出腳需要花較多的時間,在兩個電壓準位之間做轉換,尤其是電流負載達到飽和的情況下,更需要較多的時間。因此,我們可能需要降低測試頻率,並且將輸出腳的取樣時間,往後移動一下,以便通過測試。

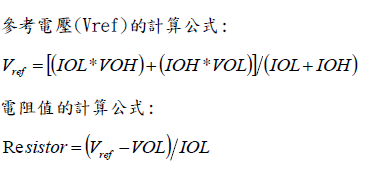

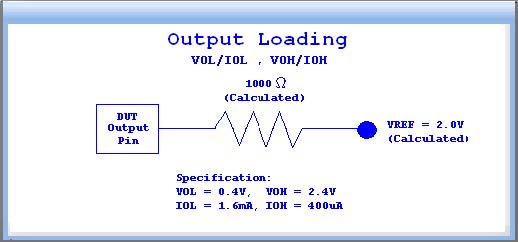

電阻性輸出負載

當你使用的測試系統,沒有提供動態負載電路時,你可能需要使用外部的電阻負載,來達到目的。這個負載,就稱為電阻性輸出負載( Resistive Output Loading)。此電阻負載,必需要能夠提供IOL/IOH的電流需求。圖17是一個單一電阻負載的範例。規格書中會定義VOL/IOL及VOH/IOH的值。而下面的公式,可以計算出參考電壓(Vref),及電阻值。

圖17

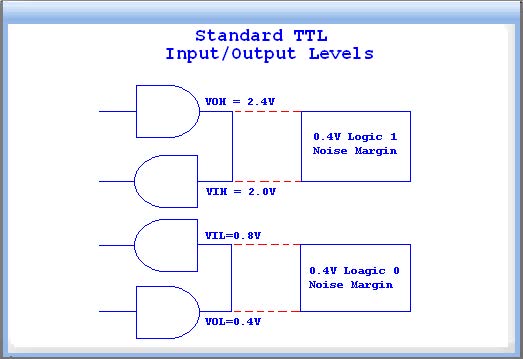

■ 輸入準位與輸出準位的關係

圖18說明了,輸入準位與輸出準位之間的關係。一般而言,輸入準位的規格為VIL=0.8V,VIH=2.0V。而VOL=0.4V,V0H=2.4V。電路的應用上,輸出腳通常會被連接到另一個電路的輸入腳上。用以上的規格測試後,我們可以認定為該電路的輸入腳與輸出腳之間,俱備400mV的Noise Margin。因為VOH被保證大於

2.4V,而VIH也被保證大於2.0V。相同的情況,存在於VOL與VIL之間。依此範例它們之間的Noise Margin也是400mV。

圖18

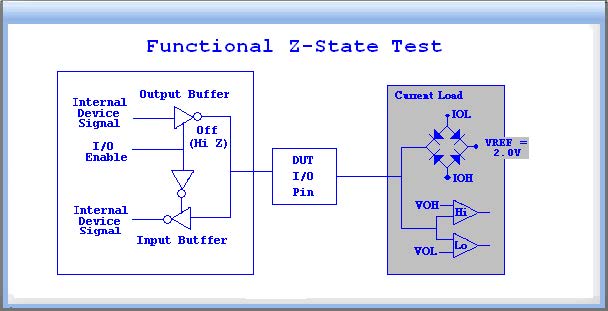

高阻抗狀態測試—測試向量法

當電路俱備雙向腳(Bi-Directional)的設計,或者稱為俱備三態輸出(Tri-State)時,在某種邏輯條件下,輸出緩衝器,必需要進入高阻抗的狀態。而這個條件,是由測試向量來決定。此時,輸出腳就會被拿來檢驗是否進入高阻抗狀態。這樣的測試,就是高阻抗狀態測試(High Impedance Testing),或者稱為Z狀態測試(Z-State Testing)。

■ 為何要做Z狀態測試呢?

Z狀態測試是要確保雙向腳俱備高阻抗的輸出能力,或者稱為輸出腳俱備關閉的能力(Off-State)。

■ Z狀態測試—測試向量法

有些測試系統,俱備測試向量法的量測能力。當執行此測試項目時,我們會用測試向量的方法來測試。此時輸出腳的三態狀況,會很動態地被驗證。

當高阻抗輸出測試,使用測試向量法時,我們需要使用到動態負載電路,或是外部電阻負載電路。而負載電路的參考電壓,需要能設定在VOL與VOH之間。通常,參考電壓會被設定為2.0V。當輸出腳進入高阻抗狀態時,它會失去吸入或供應電流的能力,或稱為浮接的狀態(Floating)。如果接上測試機的負載電路,此時輸出腳的電位,會由負載電路的參考電壓來決定。一般會將輸出腳的電位拉到1/2參考電壓值左右。此時再利用比較電路,判斷出測試結果為正確(Pass)。這裡要提醒一個觀念,也是筆者以前的一個錯誤觀念。「當雙向腳被驅動到在高阻抗狀態時,此時輸出腳的阻抗是很高的,但其電壓準位未知,並不是在1/2 VDD。因為它屬於浮接的情況。」,而要決定輸出腳的電位,是由負載電路來決定,也就是由參考電壓值來決定。我們為了讓這樣的電位,能夠通過測試,則需要將輸出電壓值,設計在VOL與VOH之間。所以高阻抗的輸出電位,是由我們設計出來的。

我們再來考慮雙向腳無法進入高阻抗的狀態。也就是輸出緩衝器無法關閉。如果輸出緩衝器無法關閉,則輸出腳會出現兩種電壓準位,一為高電位,另一為低電位。此一狀況發生後,比較電路自然可以判斷出失效的結果。圖6-19說明高阻抗測試所須的條件。

高阻抗測試的確切條件,通常會在規格書中定義,但我們仍需要一些實驗,來保證該條件下的測試是可以信賴的。當雙向腳進入高阻抗的狀態時,測試系統的負載電路,其責任需要提供一個中間的電壓準位為給雙向腳。然而,到達此中間的電壓準位的時間,是由輸出負載電流,及測試通道上的電容負載來決定。

這樣的測試條件,對於相關的測試硬體是比較敏感的。也就是不同的測試硬體,會有不同的測試結果。例如Wafer Test、Hand Test、Auto Handler Test。其原因,是因為不同的電容負載,所造成的結果。

圖19

■ 問題排除

問題排除之前,請啟動測試記錄器,並觀察測試結果。如果你有良品樣本(Golden Sample),請先對它測試一遍,並觀察測試結果。如果測試結果是失效的,我們會看到一根或更多根的輸出腳,其輸出的邏輯狀態是不正確的。如果,此測試向量只對高阻抗輸出做測試,請先將良品樣本移開,並執行測試。在未置入樣本的情況下,我們可以預期的是,其應該要通過該項測試才對。如果該測試向量,也需要判斷合法邏輯準位時,則俱備合法邏輯準位的腳位,應該要失效才對。

這項測試,會因為比較電路的VOL/VOH所影響。在電位的轉換過程中,可能需要多一些額外的時間。例如,從合法的邏輯準位,轉換成三態電位。因此,我們可能要放慢測試頻率,並往後移動輸出取樣時間,以便通過該項測試。

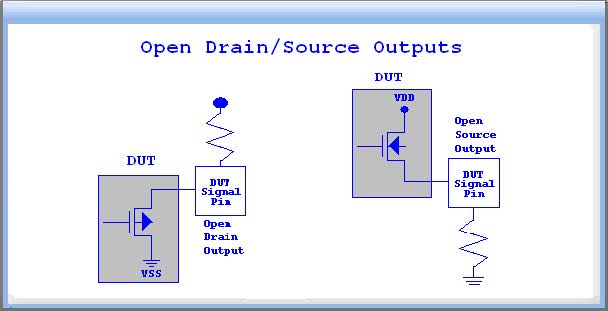

開路汲極輸出腳或開路源極輸出腳測試

通常,規格書會說明哪些輸出腳是屬於Open Drain或是Open Source的輸出腳。當你詳加檢視規格書時,請特別加以註明。因為,這些輸出腳可能需要特殊的條件,才能加以測試。例如,Open Drain輸出腳,只能被驅動在低電位。因此,它只能吸入電流。它無法被驅動到高電位,主要是因為內部電路沒有拉高電路的設計。而我們需要用外部電阻,或是負載電路來達到拉高電位的目的。

圖20

而Open Source的輸出腳,剛好與Open Drain的輸出腳相反。它們必須要被驅動在高電位,無法被驅動到低電位。它們只能夠供應電流。其道理是因為內部電路沒有拉低電路的設計。相同地,它們需要用外部電阻,或是負載電路來達到拉低電位的目的。如圖20所示,說明了何謂Open Drain的輸出腳,及何謂Open Source的輸出腳。

當此項測試以高速的測試向量法測試時,我們必需要考慮外部電阻負載的電阻值(或者是電流負載的電流值)。因為,Open Source輸出腳,由低電位轉換到高電位所需的時間,是依外部的負載電流,及相關的電容值來決定的。如果電阻太大,輸出腳沒有辦法很快地到達邏輯準位,以致於沒有辦法通過高速測試向量法的測試。

相同的地,這樣的測試條件,對於相關的測試硬體是比較敏感的。也就是不同的測試硬體,會有不同的測試結果。例如Wafer Test、Hand Test、Auto Handler Test。其原因,是因為不同的電容值,所造成的結果。